# Experiment No.3 BASIC ARITHMETIC OPERATIONS

# 1. Introduction

# 1.1 Objective:

To design and implement logic circuit for basic arithmetic operations.

# 1.2 Theory:

An important part of the central processor of any computer is the arithmetic unit in which binary addition, subtraction, division and multiplication are carried out.

Subtraction however can be performed by adding complemented numbers. Multiplication can also be performed by repeated addition .Division can be also achieved by repeated subtraction. This means that the adder is the centre piece of the arithmetic unit. There are two types of the addition:

#### 1.2.1 <u>Half - Adder (H.A) :</u>

It is a device that adds two bits of binary data. In other words, the half adder performs the operation s:

| 0 + 0 = 0 |               |       |

|-----------|---------------|-------|

| 0 + 1 = 1 |               | (1.1) |

| 1 + 0= 1  |               |       |

| 1 + 1 = 0 | , Carry $= 1$ |       |

The last operation is, of course, 1+1=0, which is 0 with a carry 1 to the next bit position. Equation (1.1) may be expressed n the form of a truth table as shown in table (1.1)

| Input |   | Output |   |

|-------|---|--------|---|

| А     | В | S      | С |

| 0     | 0 | 0      | 0 |

| 0     | 1 | 1      | 0 |

| 1     | 0 | 1      | 0 |

| 1     | 1 | 0      | 1 |

|       |   |        |   |

Table 1.1 : Truth table of Half adder

From the truth table (1.1) we see that

$$S = A\overline{B} + \overline{A}B$$

$$S = A \oplus B$$

$$C = A.B$$

(4.2)

(4.3)

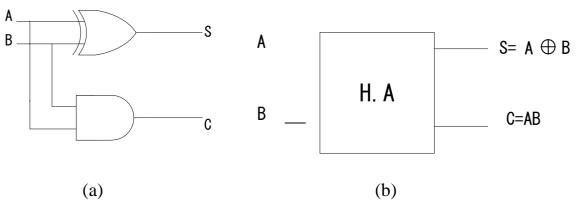

So the H.A adds only two bits at a time, so that it cannot be used to add two bits and a carry bit from a previous step, as is generally required in adding tow binary numbers the symbol for the H.A is given in Fig (1.2).

Fig. (1.2) (a) Half Adder circuit diagram

(b) Half Adder block diagram

#### 1.2.2 <u>Full-Adder (F.A):</u>

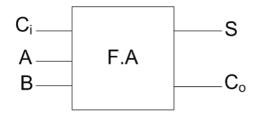

A half adder is not very useful on its own, and a third input is often required for carries. Adding numbers that have two bits or more requires a fulladder (F.A) which is capable of the previous order. The symbol of full-adder is shown in Fig. (1.3).

Fig. (1.3) Full –adder block diagram

Where:

C<sub>i</sub>: carry- in from the previous addition.

$C_{\text{o}}\colon \text{carry-} \text{ out to the next addition.}$

The truth table for a full-adder is (F.A) is determined by the 8 possible combinations of the inputs A, B and  $C_i$ , the corresponding values of S and  $C_o$  is given in table (1.2) from which we may write

| $S = \overline{A} \cdot \overline{B} \cdot C_i + \overline{A} \cdot B \cdot \overline{C_i} + A \cdot \overline{B} \cdot \overline{C_i} + A \cdot B \cdot C_i$ | <br>(4.4.a) |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| $= \left(\overline{A} \cdot \overline{B} + A \cdot B\right) \cdot C_i + \left(\overline{A} \cdot B + A \cdot \overline{B}\right) \cdot \overline{C_i}$        | <br>(4.4.b) |

| $C_o = \overline{A} \cdot B \cdot C_i + A \cdot \overline{B} \cdot C_i + A \cdot B \cdot \overline{C_i} + A \cdot B \cdot C_i$                                | <br>(4.5.a) |

| $= A \cdot B + C_i(A \oplus B)$                                                                                                                               | <br>(4.5.b) |

| Input                     | Output |    |

|---------------------------|--------|----|

| A B <i>C</i> <sub>i</sub> | S      | Co |

| 000                       | 0      | 0  |

| 001                       | 1      | 0  |

| 010                       | 1      | 0  |

| 011                       | 0      | 1  |

| 100                       | 1      | 0  |

| 101                       | 0      | 1  |

| 110                       | 0      | 1  |

| 111                       | 1      | 1  |

Table 1.2: Truth table of Full adder.

# **Procedure:**

1. Half-Adder (H.A)

a. Implement a H.A logic equation for sum and carry using NANDgates only then verify the truth table.

2. Full-Adder (F.A):

b. Verify the truth table of F.A by means of using NAND gates only.

# **Discussion:**

- 1. By means of H.A block diagram build a F.A.

- 2. Build a H.A using NOR gates only.

- 3. Use only two 2-inlput EX-OR gates and three 2-input NAND gates to build F.A.

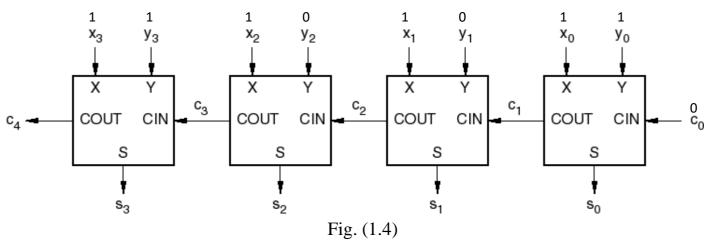

- 4. What is meant by Parallel binary adders? For the parallel adder shown in Fig (1.4), determine the sum by analysis of the logical operation of the circuit.