# Al-Mustaqbal University College Department of Intelligent medical systems First Stage

**Subject: Logic Design I**

Lecturer: Dr.Ameer Al-Khaykan

Lecture No. 4

# Logic Design I

# Dr. Ameer Al-khaykan

# **Contents**

# Contents

| 1.           | Logic Gates         | . 3 |

|--------------|---------------------|-----|

| 1.1.         | AND Gate            | .3  |

| 1.2.         | OR Gate             | .4  |

| 1.3.         | NOT Gate (Inverter) | .4  |

| 1.4.         | NAND Gate           | .5  |

| 1.5.         | NOR Gate            | .5  |

| 1.6.         | XOR Gate            | .6  |

| <b>1.7</b> . | XNOR Gate           | . 7 |

## 1. Logic Gates

A logic gate is a basic building block of a digital circuit that has two inputs and one output. The relationship between the i/p and the o/p is based on a certain logic. These gates are implemented using electronic switches like transistors, diodes. But, in practice basic logic gates are built using CMOS technology, FETS and MOSFET(Metal Oxide Semiconductor FET)s. Logic gates are used in microprocessors, microcontrollers, embedded system applications and in electronic and electrical project circuits. The basic logic gates are categorized into seven: AND, OR, XOR, NAND, NOR, XNOR and NOT.

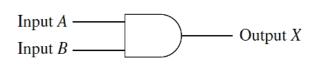

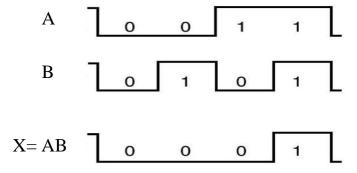

#### 1.1. AND Gate

The AND gate is an electronic circuit that gives a **high** output (1) only if **all** its inputs are high.

| Truth Table for a Two-Input AND Gate |   |        |

|--------------------------------------|---|--------|

| Input                                |   | Output |

| A                                    | В | X = AB |

| 0                                    | 0 | 0      |

| 0                                    | 1 | 0      |

| 1                                    | 0 | 0      |

| 1                                    | 1 | 1      |

Figure below shows timing diagram for AND gate with  $A = (0011)_2$ ,  $B = (0101)_2$

Logic Design I

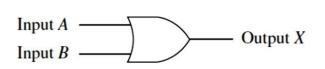

#### **1.2. OR Gate**

The OR gate is an electronic circuit that gives a high output (1) if **one or more** of its inputs are high. A plus (+) is used to show the OR operation.

| Truth Table for a Two-Input OR Gate |   |           |

|-------------------------------------|---|-----------|

| Input                               |   | Output    |

| A                                   | В | X = A + B |

| 0                                   | 0 | 0         |

| 0                                   | 1 | 1         |

| 1                                   | 0 | 1         |

| 1                                   | 1 | 1         |

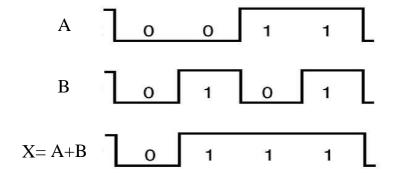

Figure below shows timing diagram for OR gate with  $A = (1100)_2$ ,  $B = (1010)_2$

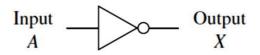

## 1.3. NOT Gate (Inverter)

The inverter is used to complement, or invert, a digital signal. It has a single input and a single output. If a HIGH level (1) comes in, it produces a Low-level (0) output. If a LOW level (0) comes in, it produces a High-level (1) output.

| <b>Truth Table for NOT Gate</b> |              |  |

|---------------------------------|--------------|--|

| Input                           | Output       |  |

| A                               | <b>X</b> = A |  |

| 0                               | 1            |  |

| 1                               | 0            |  |

Logic Design I

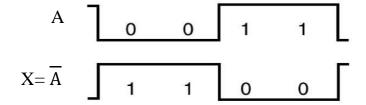

Figure below shows timing diagram for NOT gate with  $A = (1100)_2$ ,  $B = (1010)_2$

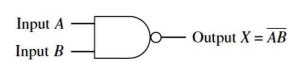

#### 1.4. NAND Gate

This gate can be considered as a NOT-AND gate which is equal to an AND gate followed by a NOT gate. The outputs of all NAND gates are high if any of the inputs are low. The symbol is an AND gate with a small circle on the output. The small circle represents inversion.

| Truth table for a Two-Input NAND Gate |   |                     |

|---------------------------------------|---|---------------------|

| Input                                 |   | Output              |

| A                                     | В | $X = \overline{A}B$ |

| 0                                     | 0 | 1                   |

| 0                                     | 1 | 1                   |

| 1                                     | 0 | 1                   |

| 1                                     | 1 | 0                   |

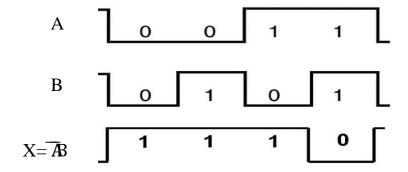

Figure below shows timing diagram for NAND gate with  $A = (1100)_2$ ,  $B = (1010)_2$

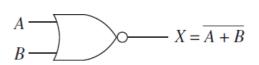

#### 1.5. NOR Gate

This is a NOT-OR gate which is equal to an OR gate followed by a NOT gate. The outputs of all NOR gates are low if any of the inputs are high.

The symbol is an OR gate with a small circle on the output. The small circle represents inversion.

| Truth table for a Two-Input NOR Gate |   |                     |

|--------------------------------------|---|---------------------|

| Input                                |   | Output              |

| A                                    | В | $X = \overline{A}B$ |

| 0                                    | 0 | 1                   |

| 0                                    | 1 | 0                   |

| 1                                    | 0 | 0                   |

| 1                                    | 1 | 0                   |

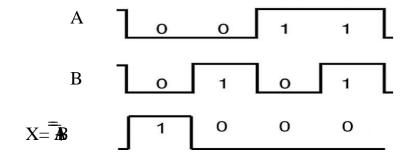

Figure below shows timing diagram for NOR gate with  $A = (1100)_2$ ,  $B = (1010)_2$

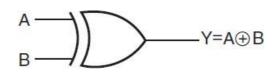

#### 1.6. XOR Gate

The 'Exclusive-OR' gate is a circuit which will give a high output if either, but not both, of its two inputs are high. An encircled plus sign ⊕ is used to show the Exclusive -OR operation.

| Truth table for a Two-Input XOR Gate |     |                  |

|--------------------------------------|-----|------------------|

| In                                   | put | Output           |

| A                                    | В   | $X = A \oplus B$ |

| 0                                    | 0   | 0                |

| 0                                    | 1   | 1                |

| 1                                    | 0   | 1                |

| 1                                    | 1   | 0                |

Logic Design I

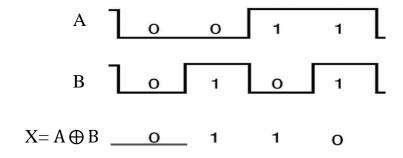

Figure below shows timing diagram for XOR gate with  $A = (1100)_2$ ,  $B = (1010)_2$

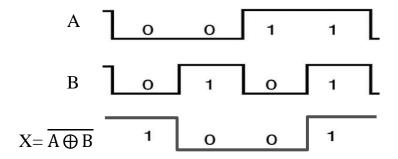

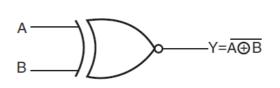

#### 1.7. XNOR Gate

The 'Exclusive-NOR' gate circuit does the opposite to the EOR gate. It will give a low output if either, but not both, of its two inputs are high. The symbol is an EXOR gate with a small circle on the output. The small circle represents inversion.

| Truth Table for a Two-Input XNOR Gate |   |                           |

|---------------------------------------|---|---------------------------|

| Input                                 |   | Output                    |

| A                                     | В | $X = \overline{A} \oplus$ |

| 0                                     | 0 | 1                         |

| 0                                     | 1 | 0                         |

| 1                                     | 0 | 0                         |

| 1                                     | 1 | 1                         |

Figure below shows timing diagram for XNOR gate with  $A = (1100)_2$ ,  $B = (1010)_2$