# Real Time System Third Level Lecture Ten

## 8155/8156 Multipurpose Programmable Devices

Dr. Hussein Abdul Almeer Alkhamees

Hussein.Alkhamees@uomus.edu.iq

Goals

Up-on completing this lecture, the student should be able to:

<sup>1-</sup> Identify the concepts behind programmable devices

<sup>2-</sup> Utilize the programmable devices into the RT designs.

#### **Programmable Interface Devices**

- Used to interface an I/O device to the microprocessor.

- Can be programmed/configured to perform various I/O functions by writing software instructions.

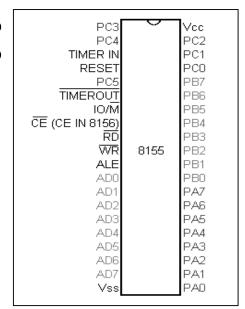

#### 8155/8156 – A Multipurpose Programmable Interface

Its programmable interface device used to interface I/O device to  $\mu P$ , its multifunction device, contain RAM, I/O ports, and timer.

- Designed to be compatible with 8085.

- It includes:

- 256 bytes of Read/Write memory.

- Three I/O ports (programmable I/O):

- o Port A (8-bit).

- o Port B (8-bit).

- o Port C (6-bit).

- A 14-bit timer.

#### **BLOCK DIAGRAM - 8155**

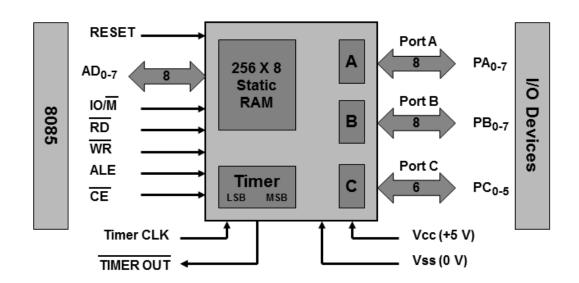

#### The 8155/8156 is a device with two sections:

- The first is 256 byte static memory (RAM).

- The second is programmable I/O ports.

Functionally the two sections is used as two independence chips, the I/O section include two 8 bit parallel I/O ports (A, B), and one 6 bit port (C), and bit timer, all ports can be simply configured as I/O ports.

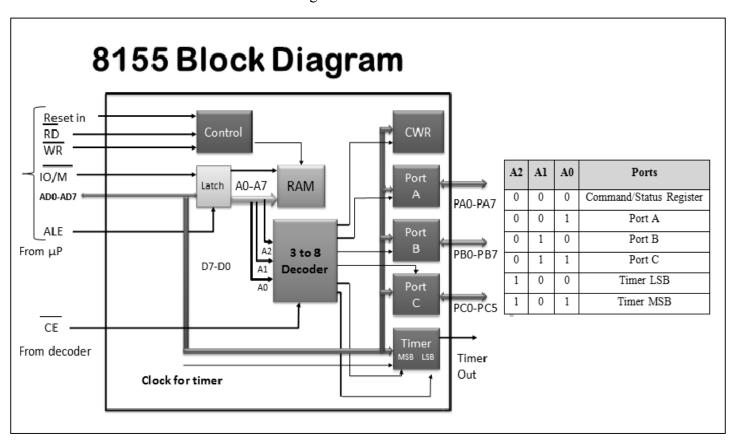

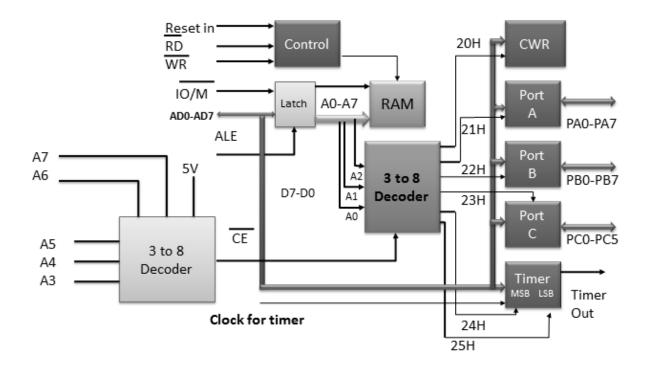

- 8155 block diagram shows 5 control signals, all except (CE) are input signal directly generated by the processor; the (CE) is input from decoder.

- o CE: chip enable, connected to the decoder.

- IO/M: specify whether the memory section is selected, or I/O section (include timer) is selected.

- ALE: address latch enable.

- o RD and WR

- RESET: connect to the RESET out of processor used to reset the chip and initializes I/O ports as input.

- In 8155 we have control register, 3 I/O ports, and 2 register for timer, so we need 3 address lines to decode there register.

#### How to Calculate Address of control register and I/O Ports of 8155?

By using 3 to 8 decoder 8205 which have 3 enables.

#### Why and How?

| ADDRESS |    | ENABLE |     |     | OUTPUTS |     |   |   |   |   |   |    |   |

|---------|----|--------|-----|-----|---------|-----|---|---|---|---|---|----|---|

| A       | A  | Α      | £,  | E 2 | E 3     | 0   | 1 | 2 | 3 | 4 | 5 | 6  | 7 |

| Ļ       | L  | ī      | L   | ī   | н       | ı   | н | н | Н | н | н | н  | н |

| н       | L  | L      | L   | L   | н       | н   | L | н | н | H | н | н  | H |

| L.      | н  | L      | L   | L   | н       | н   | н | L | н | н | н | н  | H |

| н       | н  | Ļ.     | L   | L.  | н       | н   | н | н | L | н | н | н  | н |

| L       | £. | н      | ١.  | L   | H       | 14  | н | н | н | L | н | 11 | н |

| Ή.      | L  | н      | L   | Ł   | н       | н   | н | н | н | н | L | н  | н |

| L       | н  | н      | L   | L   | н       | н   | н | н | н | н | H | L  | н |

| н       | н  | H      | L   | L   | H       | H   | н | н | н | н | н | н  | L |

| х       | ×  | ×      | L.  | L   | L       | H   | н | H | н | н | н | н  | н |

| ×       | ×  | ×      | н   | L   | L       | н   | н | н | н | н | н | н  | н |

| ×       | ×  | ×      | L   | н   | L       | н   | н | н | н | н | н | н  | н |

| x       | ×  | ×      | н   | н   | L       | i H | н | н | н | н | н | н  | н |

| ×       | x  | ×      | н   | L   | н       | н   | н | н | н | н | н | н  | н |

| ×       | ×  | ×      | Į L | н   | н       | н   | н | н | н | н | н | н  | H |

| ×       | ×  | ×      | н   | н   | н       | н   | н | н | н | H | н | н  | н |

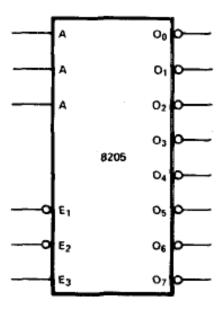

Figure 1. Logic Symbol

An 8205 it's a binary decoder (high speed 1 out of 8 binary decoder), it have 3 enable (E1, E2, E3), to enable this decoder, the E1, 2 must be low and E3 must be high. The active output pin of this decoder is low.

Ex: determine the address of the control/status, I/O ports and timer register in the following fig.?

Ex: design (draw) and determine the address of the control/status, I/O ports and timer register of the 8155 if the output of decoder O2?

#### **Application design with 8155:**

- Interfacing 8155 with 8085.

- Programming 8155.

Ex: design a full system contains microprocessor and 8155 and I/O device with its connections and shows how can any output of the decoder active the interfacing proses by using 8205?

#### What type of Commands can be given to 8155?

- To configure the I/O ports as Input or Output.

- To start/stop timer.

- To use handshake mode or not.

#### **Programming 8155:**

- 8155 is a Programmable Peripheral Interface.

- 8085 can send data to 8155 using data bus.

- This data can be:

- o For I/O devices connected to 8155.

- o Timer registers of 8155.

- o Instruction/Command word for 8155.

- Commands for 8155 are stored in an 8-bit Control Register inside 8155.

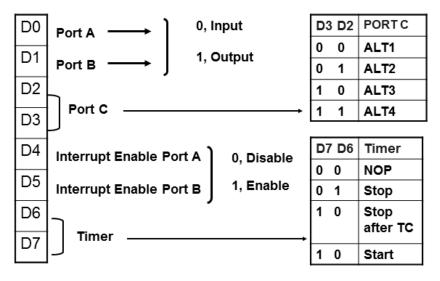

#### Control word for 8155:-

- A command/instruction for 8155 is also called control word.

- This control word is written to control register of 8155.

- Control word of 8155 is of 8-bits.

#### **Control word (command reg) format**

- 00: No effect

STB = Strobe

- 01: Stop if running else no effect

- 10: Stop after terminal count (TC) if running, else no effect

- 11: Start if not running.

### I/O functions of Port C

| ALT  | D3 | D2 | PC5  | PC4             | PC3               | PC2  | PC1             | PC0               |

|------|----|----|------|-----------------|-------------------|------|-----------------|-------------------|

| ALT1 | 0  | 0  | I    |                 | I                 |      |                 | I                 |

| ALT2 | 0  | 1  | 0    | 0               | 0                 | 0    | 0               | 0                 |

| ALT3 | 1  | 0  | 0    | 0               | 0                 | STBA | BFA             | INTR <sub>A</sub> |

| ALT4 | 1  | 1  | STBB | BF <sub>B</sub> | INTR <sub>B</sub> | STBA | BF <sub>A</sub> | INTR <sub>A</sub> |

I = Input O = Output

INTR = Interrupt Request

BF = Buffer Full

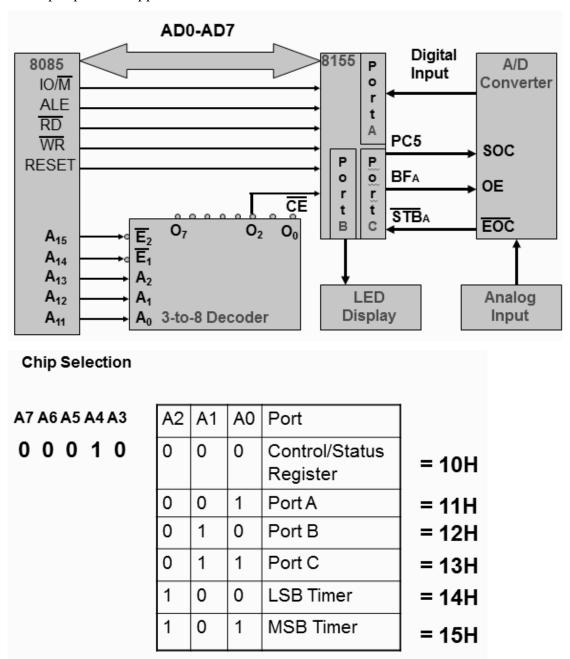

**Ex:** Design an interfacing circuit to read data from an A/D converter using the 8155A in the peripheral mapped I/O.

#### **8155: Timers**

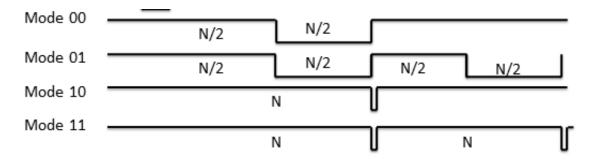

The 8155 timer consists of two 8-bit registers, 8-bit LSB and 8-bit MSB. In these 16 bits, 14 bits are used for counter and two bit for mode selection. The counter is a 14 bit down counter. It can operate in 4 different modes of operation. We can select mode using two bits M2 and M1:

• 00(Mode 0) Single Square Wave.

- 01(Mode 1) Square Wave.

- 10(Mode 2) Single Pulse on TC (terminal count).

- 11(Mode 3) Pulse every TC.

**Mode 0:** In this mode, timer gives only one cycle of square wave, the output remains high for 1/2 count and remains low for 1/2 count (N is the count value).

**Mode 1:** This mode is similar to single square wave in operation but the when counter becomes zero, the count value is automatically reloaded. Thus it provides continuous square wave.

**Mode 2:** This mode gives a single clock pulse as an output of the end of the count the output is high normally, but it becomes low for 1 clock pulse and again it will become high and remain high.

**Mode 3:** This mode is similar to mode 2 but when the counter becomes zero the count value is automatically reloaded. Thus it provides continuous pulses.

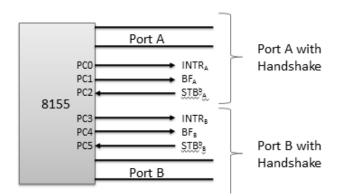

#### The 8155 I/O ports in handshake mode:

Two I/O port of 8155 (A, B) can be configured in the handshake mode, each uses there signals from port C as a control signal.

When port A configured in the handshake mode, it will uses the lower 3 signals of port C, PC0, PC1, PC2. When port B configured in the handshake mode, it will uses the upper 3 signals of port C, PC3, PC4, PC5.

The function of these signals as follows:

- STB (strobe): this is input handshake signal from peripheral to 8155.

- BF (buffer full): this is indicating the presence of the data byte in the port.

- INTR (interrupt request): this signal used to interrupt the MPU.

- INTE (interrupt enable): used to disable or enable the interrupt capability of the 8155.

#### **Status word:**

- MPU check the status Reg of port or timer.

- Control register & Status register have same port.

- Differentiated by RD and WR signals.

#### **Status word (Status reg) format:**

| D7 | D6    | D5    | D4  | D3    | D2    | D1  | D0    |

|----|-------|-------|-----|-------|-------|-----|-------|

| X  | Timer | INTEb | BFb | INTRb | INTAa | BFa | INTRa |

#### Summary:

- 1- Prog devices hugely reduce the load on CPUs.

- 2- The 8155 is the foundation prog-device and can be configured via the CWR register.

#### Questions:

- 1- What is meant by a prog-device ?

- 2- illustrate the advantage of a prog-device via a design.