Lab 4

First Stage

Cyber Security Science Department

# Computer Organization and Logic Design

# Lab 4: NAND and XOR Gates

By

Asst. Lect. Ali Saleem Haleem

## NAND and XOR Gates

#### 1. NAND Gate

- The NAND gate is a popular logic element because it can be used as a universal gate; that is, NAND gates can be used in combination to perform the AND, OR, and inverter operations.

- ✤ The NAND gate is equivalent to an AND gate followed by NOT gate

- ♦ Boolean Expression Q = A B

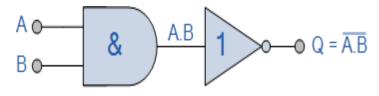

#### **1.1 Logic NAND Gate Equivalence**

2-input "AND" gate plus a "NOT" gate

The logic or Boolean expression given for a logic NAND gate is that for *Logical Addition*, which is the opposite to the AND gate, and which it performs on the *complements* of the inputs. The Boolean expression for a logic NAND gate is denoted by a single dot or full stop symbol, (.) with a line or *Overline*, ( $^-$ ) over the expression to signify the NOT or logical negation of the NAND gate giving us the Boolean expression of:  $\overline{A.B} = Q$ .

#### \* 2-input Logic NAND Gate

| Symbol                                         | ſ         | Fruth Tabl | e         |

|------------------------------------------------|-----------|------------|-----------|

|                                                | В         | А          | Q         |

| A Q                                            | 0         | 0          | 1         |

|                                                | 0         | 1          | 1         |

|                                                | 1         | 0          | 1         |

| 2-input NAND Gate                              | 1         | 1          | 0         |

| <b>Boolean Expression</b> $Q = \overline{A.B}$ | Read as A | AND B giv  | ves NOT Q |

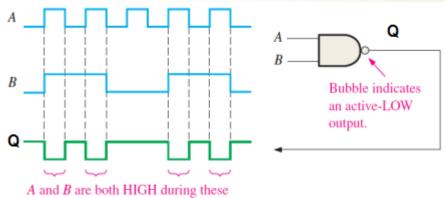

four time intervals; therefore, X is LOW.

## 3-input Logic NAND Gate

| Symbol                                           |           | Truth   | Table     |          |

|--------------------------------------------------|-----------|---------|-----------|----------|

|                                                  | С         | В       | А         | Q        |

|                                                  | 0         | 0       | 0         | 1        |

|                                                  | 0         | 0       | 1         | 1        |

|                                                  | 0         | 1       | 0         | 1        |

| 3-input NAND Gate                                | 0         | 1       | 1         | 1        |

|                                                  | 1         | 0       | 0         | 1        |

|                                                  | 1         | 0       | 1         | 1        |

|                                                  | 1         | 1       | 0         | 1        |

|                                                  | 1         | 1       | 1         | 0        |

| <b>Boolean Expression</b> $Q = \overline{A.B.C}$ | Read as A | AND B A | ND C give | es NOT Q |

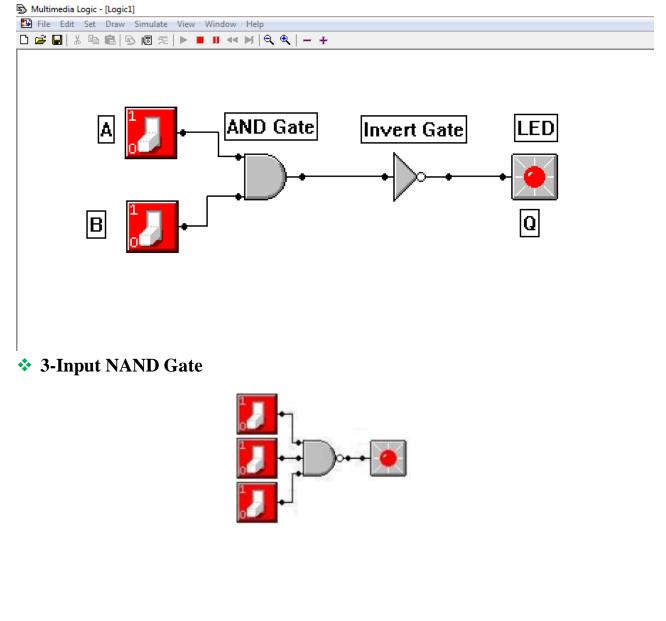

## **1.2 Implementation**

# 1. AND gate with check Invert Output (NAND)

| And Gate Properties     Impute     Impute </th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AND Gate Properties       Imputs       Imputs |

| B File Edit Set Draw Simulate View Window Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

#### **Truth Table**

| Swi | tches | LED             |

|-----|-------|-----------------|

| 0   | 0     | Lit / 1         |

| 0   | 1     | Lit / 1         |

| 1   | 0     | Lit / 1         |

| 1   | 1     | <b>Dark / 0</b> |

NAND is short for Negative And. This gate combines an And Gate with its output connected through an Inverter Gate in one device. It will output a "0" only if both its inputs are a "1"

#### 2. Use AND + NOT Gate

#### **Truth Table**

| Swit | ches |   | LED             |

|------|------|---|-----------------|

| 0    | 0    | 0 | Lit / 1         |

| 0    | 0    | 1 | Lit / 1         |

| 0    | 1    | 0 | Lit / 1         |

| 0    | 1    | 1 | Lit / 1         |

| 1    | 0    | 0 | Lit / 1         |

| 1    | 0    | 1 | Lit / 1         |

| 1    | 1    | 0 | Lit / 1         |

| 1    | 1    | 1 | <b>Dark / 0</b> |

This gate will output a "0" only if all of its inputs are a "1"

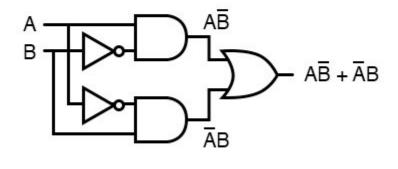

#### 2. The Exclusive-OR Gate (XOR Gate)

The exclusive-OR gate performs modulo-2 addition. Standard symbols for an exclusive OR (X-OR) gate and Boolean expression for the output of a 2-input XOR gate can be written as:

$$Q = \overline{A}B + A\overline{B} = A \oplus B$$

... is equivalent to ...

$A \oplus B = A\overline{B} + \overline{A}B$

The X-OR gate has only two inputs. The four possible input combinations and the

resulting outputs for an X-OR gate. The operation of an X-OR gate is summarized in the truth table shown

| Symbol                                  |                         | Fruth Table        | e                 |

|-----------------------------------------|-------------------------|--------------------|-------------------|

|                                         | В                       | А                  | Q                 |

| A a d d d d d d d d d d d d d d d d d d | 0                       | 0                  | 0                 |

|                                         | 0                       | 1                  | 1                 |

|                                         | 1                       | 0                  | 1                 |

| 2-input Ex-OR Gate                      | 1                       | 1                  | 0                 |

| Boolean Expression $Q = A \oplus B$     | A OR B bu               | at NOT <b>BO</b> T | <b>FH</b> gives Q |

| LOW (0) LOW (0)                         | LOW (0) -<br>HIGH (1) - |                    | HIGH (1)          |

| $HIGH (1) \longrightarrow HIGH (1)$     | HIGH (1) -              | -                  |                   |

### (Homework)

Giving the Boolean expression of:

$$Q = \overline{ABC} + AB\overline{C} + A \oplus B \oplus C$$

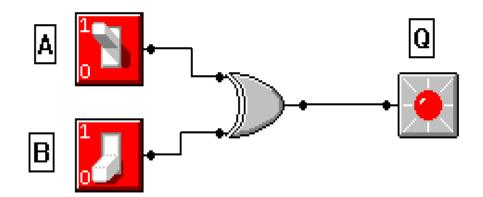

## 2.1 Implementation

| gic · | [Logic2]                           |  |

|-------|------------------------------------|--|

| Set   | Draw Simulate View Window Help     |  |

| Þ     | Ê  S @ ☆   ► ■ II << ▶   < <   − + |  |

## **Truth Table**

| Swit | ches | LED      |

|------|------|----------|

| 0    | 0    | Dark / 0 |

| 0    | 1    | Lit / 1  |

| 1    | 0    | Lit / 1  |

| 1    | 1    | Dark / 0 |

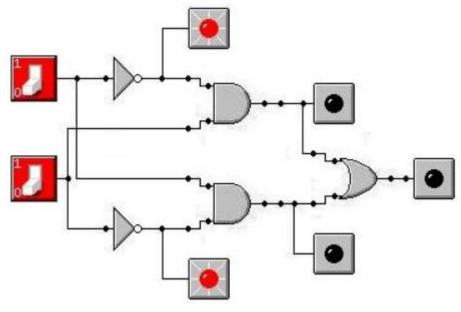

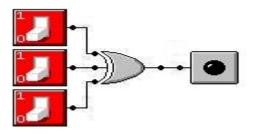

## 3-Input XOR Gate

| Switches |   |   | LED      |

|----------|---|---|----------|

| 0        | 0 | 0 | Dark / 0 |

| 0        | 0 | 1 | Lit / 1  |

| 0        | 1 | 0 | Lit / 1  |

| 0        | 1 | 1 | Dark / 0 |

| 1        | 0 | 0 | Lit / 1  |

| 1        | 0 | 1 | Dark / 0 |

| 1        | 1 | 0 | Dark / 0 |

| 1        | 1 | 1 | Lit / 1  |

XOR is short for Exclusive Or. This gate will output a "1" if only one or all of its inputs are a "1"

## 2.2 XOR Circuit