# Part I Lectures 1-7 Diode Circuit Applications

#### The PN Junction Diode

#### **Basic Construction:**

When acceptor impurities are introduced into one side and donors into the other side of a single crystal of a semiconductor, a p-n junction is formed. In general, the acceptor ion is indicated by a minus sign because, after this atom "accepts" an electron, it becomes a negative ion. The donor ion is represented by a plus sign because, after this impurity atom "donates" an electron, it becomes a positive ion. Now, if a junction is formed between a sample of p-type and one of an n-type semiconductor, this combination possesses the properties of a rectifier (permits the flow of charge in one direction). Such a two-terminal device is called a p-n junction diode.

- The two single crystal semiconductors (having four valence electrons) used most frequently in the construction of p-n junction diodes are silicon (Si) and germanium (Ge).

- The p-type is created by introducing those impurity elements (acceptors) that have three valence electrons (trivalent), such as boron, gallium, and indium.

- The n-type is created by introducing those impurity elements (donors) that have five valence electrons (pentavalent), such as antimony, arsenic, and phosphorus.

- In a p-type material the hole is the majority carrier and the electron is the minority carrier.

- In an n-type material the electron is called the majority carrier and the hole the minority carrier.

- The electrons and holes in the region of the junction will combine, resulting in a lack of carriers in the region near the junction. This region of uncovered positive and negative ions is called the "depletion region" due to the depletion of carriers in this region.

#### **Essential Characteristics:**

The essential electrical characteristic of a p-n junction is that it constitutes a rectifier which permits the easy flow of charge in one direction but restrains the flow in the opposite direction. We consider now how this diode rectifier action comes above.

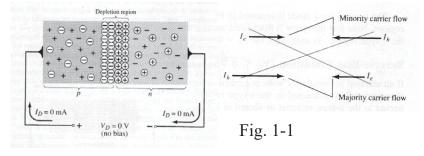

# No Applied Bias $(V_D = 0 \text{ V})$ :

In the absence of an applied bias voltage, the net flow of charge in any one direction for a semiconductor diode is zero (see Fig. 1-1).

# Reverse Bias ( $V_D < 0 \text{ V}$ ):

The current that exists under reverse-bias conditions is called the reverse saturation current and is represented by  $I_s$  (see Fig. 1-2).

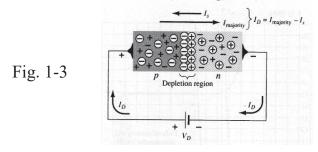

## Forward Bias $(V_D > 0 \text{ V})$ :

A semiconductor diode is forward-biased when the association p-type and positive and n-type and negative has been established (see Fig. 1-3).

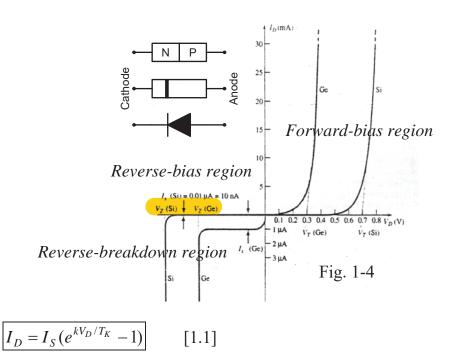

# **I-V Characteristic Carve and Current Equation:**

Where  $k = 11600/\eta$  with  $\eta = 1$  for Ge and  $\eta = 2$  for Si for relatively low levels of diode current and  $\eta = 1$  for Ge and Si for higher levels of diode current.  $T_K = T_C + 273^\circ$ .

#### **Resistance Levels:**

#### 1. DC or Static Resistance:

The application of a dc voltage to a circuit containing a p-n junction diode will result in an operating point on the characteristic carve that will not change with time. The resistance of the diode at the operating point can found simply by finding the corresponding levels of  $V_D$  and  $I_D$  as shown in Fig. 1-5 and applying the following equation:

$$R_D = \frac{V_D}{I_D}$$

[1.2]

#### 2. Ac or Dynamic Resistance:

If a sinusoidal rather than dc input is applied, the varying input will move the instantaneous operating point up and down a region of the characteristics and thus defines a specific change in current and voltage as shown in Fig. 1-6. With no applied varying signal, the point of operation would be the *Q*-point determined by the applied dc levels. A straight line drawn tangent to the curve through the *Q*-point will define a particular change in voltage and current that can be used to determine the ac or dynamic resistance for this region of the diode characteristics. In equation form,

$$r_d = \frac{\Delta V_d}{\Delta I_d}$$

[1.3]

Diode characteristic

Tangent line

Q-point (dc operation)

Pig. 1-6

In differential calculus, the derivative of a function at a point is equal to the slope of the tangent line drawn at that point. Eq. [1.3], as defined by Fig. 1-6, is, therefore, essentially finding the derivative of the function at the Q-point of operation. If we find the derivative of the general Eq. [1.1] for the p-n junction diode with respect to the applied forward bias and then invert the result, we will have an equation for the dynamic or ac resistance in that region. That is;

$$\frac{d}{dV_{D}}(I_{D}) = \frac{d}{dV}[I_{S}(e^{kV_{D}/T_{K}} - 1)]$$

$$\frac{dI_{D}}{dV_{D}} = \frac{k}{T_{K}}(I_{D} + I_{S})$$

$$\frac{dI_{D}}{dV_{D}} \cong \frac{k}{T_{K}}I_{D} \qquad (Generally, I_{D} >> I_{S})$$

$$\frac{dI_{D}}{dV_{D}} = 38.93I_{D} \qquad (\eta = 1 \& T_{K} = 298^{\circ} \Rightarrow \frac{K}{T_{K}} = \frac{11600}{298} \cong 38.93)$$

$$r = v/i = \frac{dV_{D}}{dI_{D}} \cong \frac{0.026}{I_{D}}$$

$$[1.4]$$

All the resistance levels determined thus far have been defined by the p-n junction and do not include the resistance of the semiconductor material itself (called **body resistance**) and the resistance introduce by the connection between the semiconductor material and the external metallic conductor (called **contact resistance**). These additional resistance levels can be included in Eq. [1.4] by adding resistance denoted by  $r_B$  appearing in Eq. [1.5].

$$r_d' = \frac{26mV}{I_D} + r_B$$

[1.5]

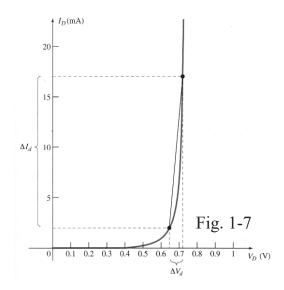

#### 3. Average AC Resistance:

If the input signal is sufficiently large to produce a board swing such as indicated in Fig. 1-7, the resistance associated with the device for this region is called the average ac resistance. The average ac resistance is, by definition, the resistance determined by a straight line drawn between the two intersection establish by the maximum and minimum value of input voltage. In equation form,

$$\left| r_{av} = \frac{\Delta V_d}{\Delta I_d} \right|_{pt. to \ pt.}$$

[1.6]

# **Equivalent Circuits (Models):**

## 1. Piecewise-Linear Model: (see Fig.1-8);

Forward-bias;

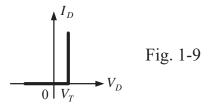

# **2. Simplified Model:** (see Fig. 1-9);

Forward-bias &  $R_{network} >> r_{av(F)}$ ;

$$+V_D - +V_T - - +V_T - - +V_D - +V_T - +V_D - +V_$$

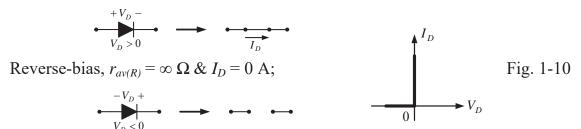

Reverse-bias,

$$r_{av(R)} = \infty \Omega \& I_D = 0 \text{ A};$$

$$V_D + V_D + V_D$$

## 3. Ideal Model: (see Fig. 1-9);

Forward-bias,  $E_{network} \gg V_T$ ,  $R_{network} \gg r_{av(F)} \& V_D = 0 \text{ V}$ ;

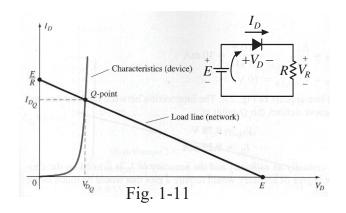

## **Load-Line Analysis:**

$$E - V_D - V_R = 0$$

$$E = V_D + I_D R$$

$$I_D = -\frac{V_D}{R} + \frac{E}{R}$$

[1.7]

Eq. [1.7] is a linear equation; y = mx + c,

where

$$m = -1/R$$

&  $c = E/R$ .

$$I_D = 0 \Rightarrow V_D = E$$

$$V_D = 0 \Rightarrow I_D = \frac{E}{R}$$

[1.8]

# Example 1-1:

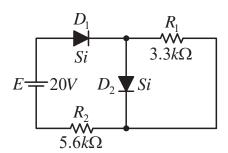

Determine the currents  $I_{D_1}$ ,  $I_{D_2}$ , and  $I_{R_1}$  for the network of Fig. 1-12.

Fig. 1-12

Solution:

$$I_{R_1} = \frac{V_{D_2}}{R_1} = \frac{0.7}{3.3k} = 0.212mA.$$

Appling KVL yields:

$$-V_{R_2} + E - V_{D_1} - V_{D_2} = 0$$

and

$$V_{R_2} = E - V_{D_1} - V_{D_2} = 20 - 0.7 - 0.7 = 18.6V$$

,

with

$$I_{D_1} = \frac{V_{R_2}}{R_2} = \frac{18.6}{5.6k} = 3.32 \text{ mA}.$$

Finally,

$$I_{D_2} = I_{D_1} - I_{R_1} = 3.32m - 0.212m = 3.108mA$$

.