### **Lecture Two**

### Logic gates

The **logic gate** is the basic building block in digital systems. Logic gates operate with binary numbers. Gates are therefore referred to as binary logic gates. All voltages used with logic gates will be either HIGH or LOW. In this lecture, a HIGH voltage will mean a binary 1, and a LOW voltage will mean a binary 0. Remember that logic gates are electronic circuits.

All digital systems are constructed by using only three basic logic gates.

### These basic gates are:

- 1- AND gate,

- **2- OR** gate,

- **3- NOT** gate.

### 1- THE AND GATE

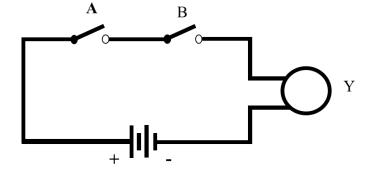

The AND gate is called the "all or nothing" gate. The schematic in Fig. 1 shows the idea of the AND gate. The lamp (Y) will light only when both input switches (A and B) are closed.

| Input<br>Switches |       | Output<br>Light |

|-------------------|-------|-----------------|

| В                 | A     | Y               |

| open              | open  | no              |

| open              | close | no              |

| close             | open  | no              |

| close             | close | yes             |

Figure 1.

The standard logic symbol for the AND gate is drawn in Fig. 2. This symbol shows the inputs as A and B. The output is shown as Y. This is the symbol for a 2-input **AND** gate. The truth table for the 2-input AND gate is shown in Fig. 2. Note that only when both input A and input B are 1 will the output be 1.

**A truth table** defines the logical outputs (0 or 1) of a logic gate for all possible combinations of logical inputs

| Input |   | Output |

|-------|---|--------|

| В     | A | Y      |

| 0     | 0 | 0      |

| 0     | 1 | 0      |

| 1     | 0 | 0      |

| 1     | 1 | 1      |

(a) truth table

(b) AND-gate symbol

Figure 2

Boolean algebra is a form of symbolic logic that shows how logic gates operate. A Boolean expression is a "shorthand" method of showing what is happening in a logic circuit.

$$A \cdot B = Y$$

The Boolean expression is read as A AND (. means AND) B equals the output Y. The dot (.) means the logic function AND in Boolean algebra, not multiply as in regular algebra, Sometimes the dot (.) is left out of the Boolean expression. The Boolean expression for the 2-input AND gate is then:

$$AB = Y$$

The Boolean expression reads *A* AND *B* equals the output *Y*.

Example:

### 1- Write the Boolean expression for a 3-input AND gate

Solution:

$$A \cdot B \cdot C = Y$$

or  $A B C = Y$

### 2- Draw the logic symbol for a 3-input AND gate.

Solution:

### 3- Draw a truth table for a 3-input AND gate.

|   | Input |   | Output |

|---|-------|---|--------|

| С | В     | A | y      |

| 0 | 0     | 0 | 0      |

| 0 | 0     | 1 | 0      |

| 0 | 1     | 0 | 0      |

| 0 | 1     | 1 | 0      |

| 1 | 0     | 0 | 0      |

| 1 | 0     | 1 | 0      |

| 1 | 1     | 0 | 0      |

| 1 | 1     | 1 | 1      |

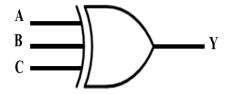

#### 2- THE OR GATE

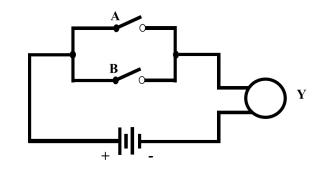

The OR gate is called the "any or all" gate. The schematic in Fig. 3 shows the idea of the OR gate. The lamp (Y) will glow when either switch A or switch B is closed. The lamp will also glow when both switches A and B are closed. The lamp (Y) will not glow when both switches (A and B) are open.

| Input<br>Switches |       | Output<br>Light |

|-------------------|-------|-----------------|

| В                 | A     | Y               |

| open              | open  | no              |

| open              | close | yes             |

| close             | open  | yes             |

| close             | close | yes             |

Figure 3

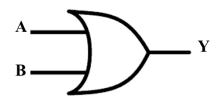

The standard logic symbol for an **OR** gate is drawn in Fig. 4. Note the different shape of the OR gate. The OR gate has two inputs labeled A and B. The output is labeled Y. The shorthand Boolean expression for this OR function is given as A + B = Y. Note that the plus (+) symbol means OR in Boolean algebra. The expression (A + B = Y) is read as A OR (+ means OR) B equals output Y.

| Input |   | Output |

|-------|---|--------|

| В     | A | Y      |

| 0     | 0 | 0      |

| 0     | 1 | 1      |

| 1     | 0 | 1      |

| 1     | 1 | 1      |

(a) truth table

(b) OR-gate symbol

Figure 4

Example:

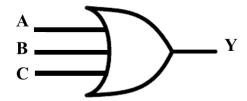

1- Write the Boolean expression for a 3-input OR gate.

Solution:

$$A + B + C = Y$$

2- Draw the logic symbol for a 3-input OR gate.

Solution

3- Draw a truth table for a 3-input OR gate.

| Input |   | Output |   |

|-------|---|--------|---|

| С     | В | A      | y |

| 0     | 0 | 0      | 0 |

| 0     | 0 | 1      | 1 |

| 0     | 1 | 0      | 1 |

| 0     | 1 | 1      | 1 |

| 1     | 0 | 0      | 1 |

| 1     | 0 | 1      | 1 |

| 1     | 1 | 0      | 1 |

| 1     | 1 | 1      | 1 |

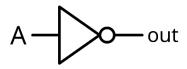

### **3- THE NOT GATE**

A NOT gate is also called an inverter. The NOT gate has only one input and one output. Figure 5 illustrates the logic symbol for the inverter, or NOT gate.

| Input | Output |

|-------|--------|

| A     | Y      |

| 0     | 1      |

| 1     | 0      |

(a) truth table

(b) NOT-gate symbol

Figure 4

The input is always changed to its opposite. **If** the input is 0, the NOT gate will give its *complement*, or opposite, which is 1. If the input to the NOT gate is a 1, the circuit will complement it to give a **0**. This inverting is also called *complementing* or *negating*.

The Boolean expression for inverting is  $A = \overline{A}$  reads as A equals the output *not* A. The bar over the A means to complement A.

### **Universal Logic Gates**

These gates can perform the functions of all other gates:

- 1- NAND Gate

- 2- NOR Gate

### 1- The NAND gate

The NAND gate is the complement of AND gate and the logic symbol of this gate is shown in fig. 5.

The Boolean expression for the entire circuit is  $\overline{A}$ .  $\overline{B}$ = Y. It is said that this is a not-AND or NAND circuit. The bubble is sometimes called an invert bubble. The invert bubble provides a simplified method of representing the NOT gate. The unique output from the NAND gate is a LOW when all inputs are HIGH.

The NAND gate is widely used in most digital systems.

| Input |   | Ou  | tput |

|-------|---|-----|------|

| В     | A | AND | NAND |

| 0     | 0 | 0   | 1    |

| 0     | 1 | 0   | 1    |

| 1     | 0 | 0   | 1    |

| 1     | 1 | 1   | 0    |

The AND- and NAND-gate truth tables

Examples:

1- Write the Boolean expression for a 3-input NAND gate.

Solution:

$$\overline{\boldsymbol{A}.\boldsymbol{B}.\boldsymbol{C}} = Y$$

or  $\overline{\boldsymbol{A}\,\boldsymbol{B}\,\boldsymbol{C}} = Y$

2- Draw the logic symbol for a 3-input NAND gate

Solution:

3- Draw the truth table for a 3-input NAND gate.

|   | Input |   | Output |

|---|-------|---|--------|

| С | В     | A | y      |

| 0 | 0     | 0 | 1      |

| 0 | 0     | 1 | 1      |

| 0 | 1     | 0 | 1      |

| 0 | 1     | 1 | 1      |

| 1 | 0     | 0 | 1      |

| 1 | 0     | 1 | 1      |

| 1 | 1     | 0 | 1      |

| 1 | 1     | 1 | 0      |

### Department of Biomedical Engineering Digital Electronics / Third stage Lecturer: Dr. Hussam Jawad Kadhim AL\_Janabi

Email: hussam.jawad@uomus.edu.iq

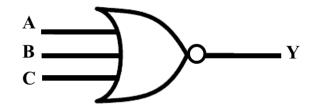

### 2- The NOR gate

The NOR gate represents the complement of the OR operation. An inverter has been connected to the output of an OR gate. Adding the overbar produces the Boolean expression  $\overline{A+B}=Y$ . The not-OR function can be drawn as a single logic symbol called a *NOR gate*. The standard symbol for the NOR gate is illustrated in Fig. 6. Note that a small invert bubble has been added to the OR symbol to form the NOR symbol.

Fig. 6 The NOR gate

The truth table of the NOR gate is show below. Note that the output column of the NOR gate is the complement (has been inverted) of the shaded OR column.

| Input |   | Ou | tput |

|-------|---|----|------|

| В     | A | OR | NOR  |

| 0     | 0 | 0  | 1    |

| 0     | 1 | 1  | 0    |

| 1     | 0 | 1  | 0    |

| 1     | 1 | 1  | 0    |

The *unique output* from the NOR gate is a **HIGH** when all inputs are LOW.

Examples:

1- Write the Boolean expression for a 3-input NOR gate.

Solution:

$$\overline{A + B + C} = Y$$

2- Draw the logic symbol for a 3-input NOR gate

Solution:

3- What is the truth table for a 3-input NOR gate?

| Input |   | Output |   |

|-------|---|--------|---|

| С     | В | A      | y |

| 0     | 0 | 0      | 1 |

| 0     | 0 | 1      | 0 |

| 0     | 1 | 0      | 0 |

| 0     | 1 | 1      | 0 |

| 1     | 0 | 0      | 0 |

| 1     | 0 | 1      | 0 |

| 1     | 1 | 0      | 0 |

| 1     | 1 | 1      | 0 |

### **Derived Logic Gates**

- 1- The Exclusive-OR gate

- 2- The Exclusive-NOR gate

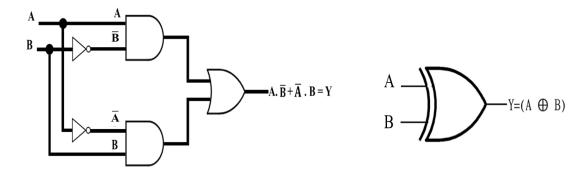

### 1- The Exclusive-OR gate

The *exclusive-OR gate* is referred to as the "any but not all" gate. The exclusive-OR term is often shortened to read as *XOR*. *A* truth table for the **XOR** function is shown in Fig. 7. Careful examination shows that this truth table is similar to the OR truth table except that when both inputs are 1, the **XOR** gate generates a 0. The **XOR** gate is enabled *only when an odd number* of *1s appears at the inputs*.

Lines 1 and 4 of the truth table contain even numbers (0,2) of 1s, and therefore the **XOR** gate is disabled and a 0 appears at the output. The XOR gate could be referred to as an odd-bit check circuit.

The Boolean expression of XOR is  $\mathbf{A} \cdot \overline{\mathbf{B}} + \overline{\mathbf{A}} \cdot \mathbf{B} = \mathbf{A} \oplus \mathbf{B}$

(a) Logic circuit that performs the XOR function

(b) Standard logic symbol for the XOR gate

Figure 7

Examples:

1- Write the Boolean expression for a 3-input XOR gate.

Solution:

$$A \oplus B \oplus C = Y$$

2- Draw the logic symbol for a 3-input XOR gate.

Solution:

3- What is the truth table for a 3-input XOR gate? Remember that an odd number of 1s generates a 1 output.

|   | Input |   | Output |

|---|-------|---|--------|

| С | В     | A | y      |

| 0 | 0     | 0 | 0      |

| 0 | 0     | 1 | 1      |

| 0 | 1     | 0 | 1      |

| 0 | 1     | 1 | 0      |

| 1 | 0     | 0 | 1      |

| 1 | 0     | 1 | 0      |

| 1 | 1     | 0 | 0      |

| 1 | 1     | 1 | 1      |

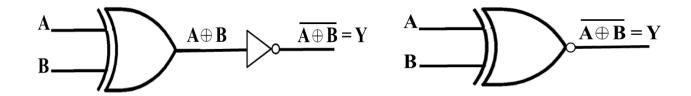

### 2- The Exclusive-NOR gate

X- NOR gate represent the complement of X-OR gate, logic symbol is shown in Fig. 8. The XOR gate produces the expression  $\mathbf{A} \oplus \mathbf{B}$ . When this is inverted, it forms the Boolean expression for the XNOR gate,  $\overline{\mathbf{A} \oplus \mathbf{B}} = \mathbf{Y}$

Figure 8

Note that all outputs of the XNOR gate are the complements of the XOR-gate outputs. While the XOR gate is an odd-number-of-1s detector, the XNOR gate detects *even numbers* of 1s. The XNOR gate will produce a 1 output when an *even number* of 1s appear at the inputs.

| Input |   | Output |      |

|-------|---|--------|------|

| В     | A | XOR    | XNOR |

| 0     | 0 | 0      | 1    |

| 0     | 1 | 1      | 0    |

| 1     | 0 | 1      | 0    |

| 1     | 1 | 0      | 1    |

The XOR and XNOR gate truth tables

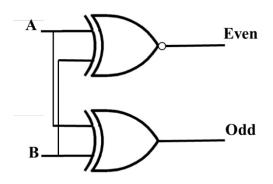

Example: For two input bits draw a logic circuit that finds the odd and even parity cheek for them.

| Input |   | Output |      |

|-------|---|--------|------|

| В     | A | Odd    | Even |

| 0     | 0 | 0      | 1    |

| 0     | 1 | 1      | 0    |

| 1     | 0 | 1      | 0    |

| 1     | 1 | 0      | 1    |