# **Types of A/D Converters**

- Flash ADC

- Delta-Sigma ADC

- Dual Slope (integrating) ADC

- Successive Approximation ADC

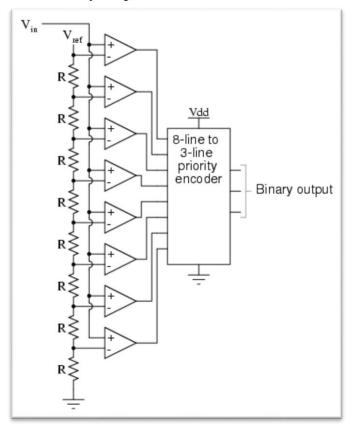

# 1. Flash A/D Converter

### **Fundamental Components**

**Resistors** use the resistors to form a ladder voltage divider, which divides the reference voltage into equal intervals.

**Comparators** Consists of a series of comparators, which comparing the input signal to a unique reference voltage.

**Priority encoder** the comparator outputs connect to the inputs of a priority encoder circuit, which produces a binary output.

#### How does it work?

- Uses the comparators to determine in which the input voltage  $V_{in}$  is exceed or not the  $V_{ref}$ .

- When the analog input voltage exceeds the reference voltage at each comparator, the comparator outputs will sequentially saturate to a high state.

- The priority encoder generates a binary number based on the highest-order active input, ignoring all other active inputs.

## **Advantages and Disadvantages**

- Simplest in terms of operational theory, most efficient in terms of speed (very fast).

- Lower resolution, Expensive, for each additional output bit, the number of comparators is increase.

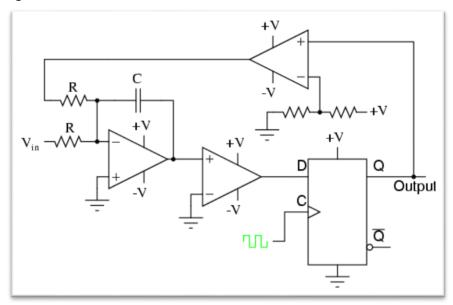

# 2. Sigma Delta ADC

## **Main Components**

- Resistors

- Integrator

- Capacitor

- Comparators

- Control Logic

#### How does it work?

- Input is over sampled, and goes to integrator.

- The integration is then compared to ground.

- Iterates and produces a serial bit stream.

- Output is a serial bit stream which is proportional to V<sub>in</sub>.

## **Advantages and Disadvantages**

- High resolution.

- Slow due to oversampling.

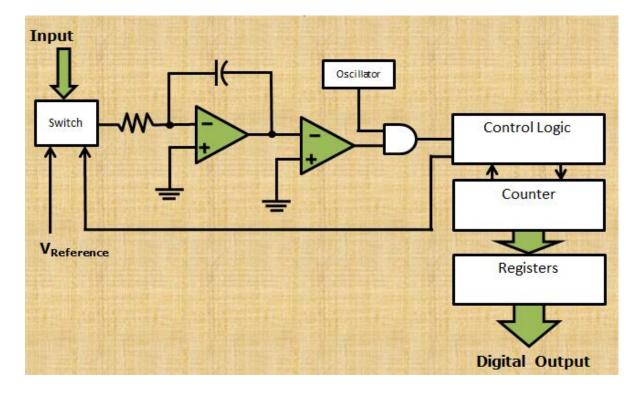

# 3. **Dual Slope Converter**

### **Fundamental components**

- Integrator

- Electronically Controlled Switches

- Counter

- Clock

- Control Logic

- Comparator

## The Dual Slope ADC functions in this manner:

- When an analog value is applied, the capacitor begins to charge in a linear manner and the oscillator passes to the counter.

- The counter continues to count until it reaches a predetermined value. Once this value is reached the count stops and the counter is reset. The control logic switches the input to the first comparator to a reference voltage, providing a discharge path for the capacitor.

- As the capacitor discharges the counter counts.

- When the capacitor voltage reaches the reference voltage the count stops and the value is stored in the register.

### **Advantages and Disadvantages**

- High Accuracy.

- Slow, Cost.

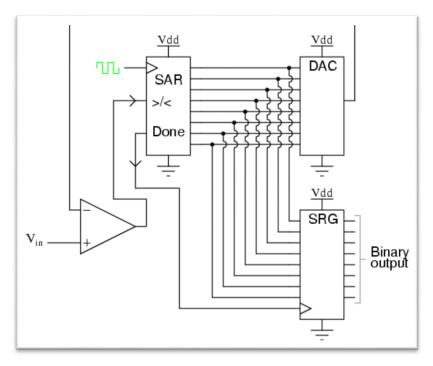

# 4. Successive Approximation ADC

- Much faster than the Dual Slope.

- A comparator and a DAC are used in the process.

- A Successive Approximation Register (SAR) is added to the circuit

- Instead of counting up in binary sequence, this register counts by trying all values of bits starting with the MSB and finishing at the LSB.

- The register monitors the comparators output to see if the binary count is greater or less than the analog signal input and adjusts the bits accordingly.

### **Advantages and Disadvantages**

- Capable of high speed and reliable, medium accuracy compared to other ADC types, Good tradeoff between speed and cost.

- Higher resolution successive approximation ADC's will be slower.

#### Example

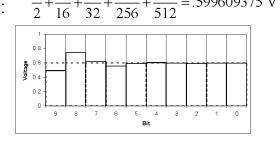

10 bit ADC,  $V_{in}$ = 0.6 volts (from analog device),  $V_{ref}$ =1 volts, Find the digital value of  $V_{in}$ ?

### Solu:

- MSB (bit 9)

- Divided V<sub>ref</sub> by 2

- Compare V<sub>ref</sub>/2 with V<sub>in</sub>

- If  $V_{in}$  is greater than  $V_{ref}/2$ , turn MSB on (1)

- If  $V_{in}$  is less than  $V_{ref}/2$ , turn MSB off (0)

- $V_{in} = 0.6V$  and V = 0.5

- Since  $V_{in}>V$ , MSB = 1 (on)

|--|

- Next Calculate MSB-1 (bit 8)

- Compare  $V_{in}=0.6 \text{ V}$  to  $V=V_{ref}/2 + V_{ref}/4 = 0.5 + 0.25 = 0.75 \text{ V}$

- Since 0.6<0.75, MSB is turned off

- Calculate MSB-2 (bit 7)

- Go back to the last voltage that caused it to be turned on (Bit 9) and add it to V<sub>ref</sub>/8, and compare with V<sub>in</sub>

- Compare  $V_{in}$  with  $(0.5+V_{ref}/8)=0.625$

- Since 0.6<0.625, MSB is turned off

| 1 | 0 | 0 |  |  |  |  |  |  |  |

|---|---|---|--|--|--|--|--|--|--|

|---|---|---|--|--|--|--|--|--|--|

- Calculate the state of MSB-3 (bit 6)

- Go to the last bit that caused it to be turned on (In this case MSB-1) and add it to  $V_{ref}/16$ , and compare it to  $V_{in}$

- Compare  $V_{in}$  to  $V = 0.5 + V_{ref}/16 = 0.5625$

- Since 0.6>0.5625, MSB-3=1 (turned on)

| MSB | MSB-1 | MSB-2 | MSB-3 |  |  |  |

|-----|-------|-------|-------|--|--|--|

| 1   | 0     | 0     | 1     |  |  |  |

- This process continues for all the remaining bits.

- •Digital Results:

| MSB | MSB-1 | MSB-2 | MSB-3 |   |   |   |   |   | LSB |

|-----|-------|-------|-------|---|---|---|---|---|-----|

| 1   | 0     | 0     | 1     | 1 | 0 | 0 | 1 | 1 | 0   |

•Results:

# **ADC Specifications:**

- Conversion time

- Resolution

- Accuracy

- Linearity

- Missing code

**ADC Errors** due to Noise and Aliasing.

### How to choose the ADC according to the resolution?

Two ways for find the resolution needed in ADC, first way is to find the **dynamic** range of input signal and to choose the number of bits based on this.

$N>=ln (V_{max}/V_{noise})$  --- dynamic range (stage) (sensor)

Another way to choose the number of bits is based on the **resolution required** in input signal.

$N>=ln (S_{max}/S_{noise})$  --- required resolutions (stage before ADC) (transducer)

#### **Example**

A transducer is to be used to find the temperature over a range of 0 to 100 C. we are required to read and display the temperature to a resolution of +- 1 C. the transducer produces a voltage from 0 to 3v over this temperature range with +-3mv noise. Specify the number of bits in ADC: a) Based on dynamic range. b) Based on required resolutions.

• **Conversion time** is the time required to complete a conversion of the input signal, in other words it's the time it takes for an analog-to-digital conversion.

$$F_{max} = \frac{1}{2* Conversion time}$$

#### Ex:

- 1. An ADC has a conversion time of 100 μs. what is the maximum frequency that can be converted?

- 2. A 1 Khz sinusoidal signal to be digitized using 8-bit ADC. Find the conversion time that can be used?

- **Resolution** is the number of bits used for conversion (8 bits, 12 bits, ...)

$$resolution = \frac{full\ Scale\ Signal}{2^n}$$

#### Ex:

An 8-bits ADC is used to digitize a five volt (5v) full scale signal. What is the resolution?

• **Quantization error** is defined as the difference between the actual analog input and the digital representation of that value.

$$\text{Maximum Quantization } (q_{max}) = \frac{A}{2^{n+1}}$$

Average Quantization

$$(q_{av}) = \frac{A}{2^{n+2}}$$

Where A is the amplitude and n is the number of bits.

#### Ex:

An analog signal of amplitude 12v is sampled with an 8bit ADC; calculate the maximum and average quantization error?