# **Lecture Seven**

# **Counters**

# 1- Asynchronous Counters

The term asynchronous refers to events that do not have a fixed time relationship with each other and, generally, do not occur at the same time. An asynchronous counter is one in which the flip-flops (FF) within the counter do not change states at exactly the same time because they do not have a common clock pulse.

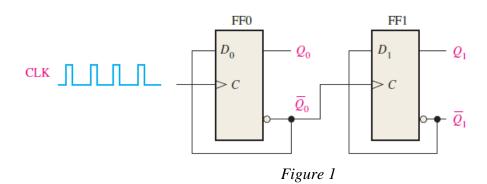

# A 2-bit Asynchronous Binary Counter

Figure 1 shows a 2-bit counter connected for asynchronous operation. Notice that the clock (CLK) is applied to the clock input (C) of *only* the first flip-flop, FF0, which is always the least significant bit (LSB). The second flip-flop, FF1, is triggered by the  $\bar{Q}_0$  output of FF0. FF0 changes state at the positive-going edge of each clock pulse, but FF1 changes only when triggered by a positive-going transition of the  $\bar{Q}_0$  output of FF0. Therefore, the two flip-flops are never simultaneously triggered, so the counter operation is asynchronous.

# **The Timing Diagram**

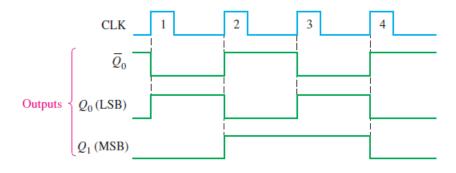

Let's examine the basic operation of the asynchronous counter of Figure 1 by applying four clock pulses to FF0 and observing the Q output of each flip-flop. Figure 2 illustrates the changes in the state of the flip-flop outputs in response to the clock pulses. Both flip-flops are connected for toggle operation  $(D = \bar{Q})$  and are assumed to be initially RESET (Q LOW).

Figure 2

Table (1): The binary state sequence for the counter in Figure 1

| Clock Pulse | $Q_1$ | $Q_2$ |

|-------------|-------|-------|

| Initially   | 0     | 0     |

| 1           | 0     | 1     |

| 2           | 1     | 0     |

| 3           | 1     | 1     |

| 4 (recycle) | 0     | 0     |

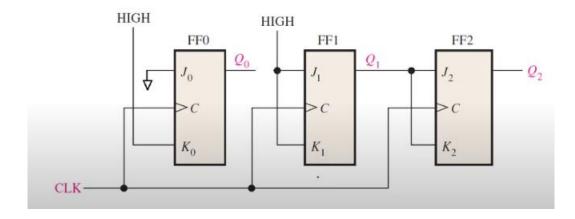

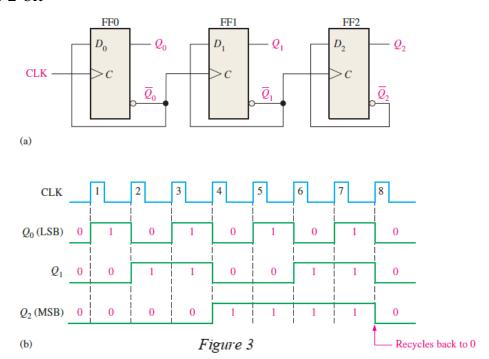

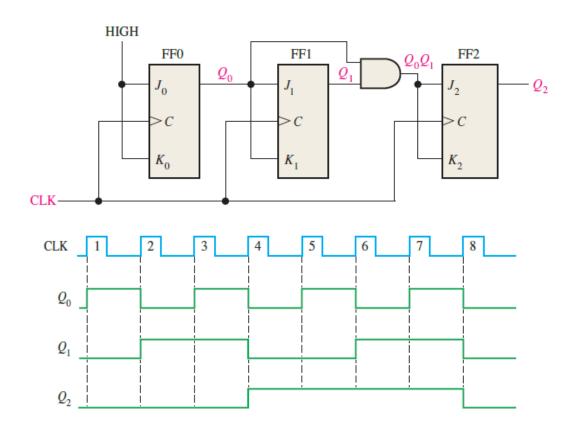

# A 3-bit Asynchronous Binary Counter

The state sequence for a 3-bit binary counter is listed in Table 2, and a 3-bit asynchronous binary counter is shown in Figure 3(a). The basic operation is the same as that of the 2-bit

Table (2): State sequence for a 3-bit binary counter

| Clock Pulse | Q2 | $Q_1$ | $Q_0$ |

|-------------|----|-------|-------|

| Initially   | 0  | 0     | 0     |

| 1           | 0  | 0     | 1     |

| 2           | 0  | 1     | 0     |

| 3           | 0  | 1     | 1     |

| 4           | 1  | 0     | 0     |

| 5           | 1  | 0     | 1     |

| 6           | 1  | 1     | 0     |

| 7           | 1  | 1     | 1     |

| 8 (recycle) | 0  | 0     | 0     |

# Example (1)

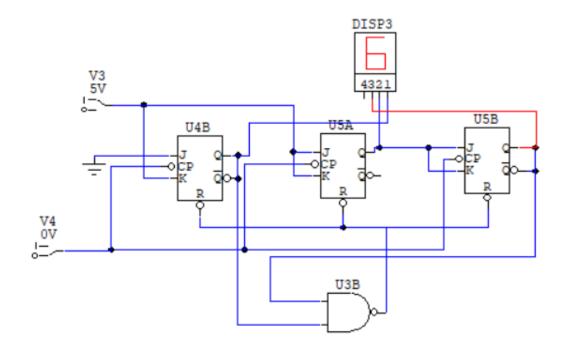

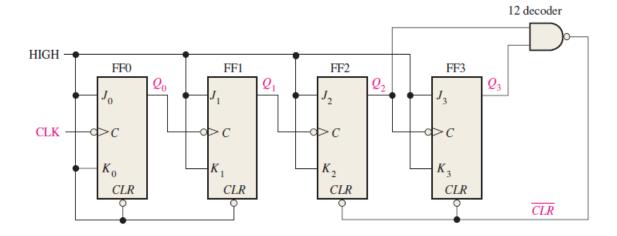

Show how an asynchronous counter with J-K flip-flops can be implemented having a modulus of twelve with a straight binary sequence from 0000 through 1011.

# **Solution**

Figure 4

### 2- Synchronous Counters

The term **synchronous** refers to events that have a fixed time relationship with each other. J-K flip-flops are used to illustrate most synchronous counters.

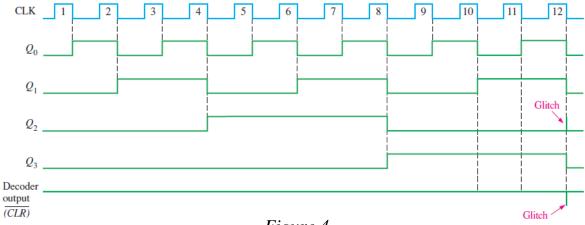

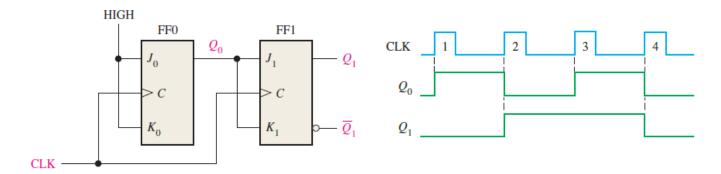

#### A 2-Bit Synchronous Binary Counter

The operation of a J-K flip-flop synchronous counter is as follows:

First, assume that the counter is initially in the binary 0 state; that is, both flipflops are RESET. When the positive edge of the first clock pulse is applied, FF0 will toggle and  $Q_0$  will therefore go HIGH. What happens to FF1 at the positive-going edge of CLK1? To find out, let's look at the input conditions of FF1. Inputs  $J_1$  and  $K_1$  are both LOW because  $Q_0$ , to which they are connected, has not yet gone HIGH. Remember, there is a propagation delay from the triggering edge of the clock pulse until the Q output actually makes a transition. So, J = 0 and K = 0 when the leading edge of the first clock pulse is applied. This is a no-change condition, and therefore FF1 does not change state

Figure 5

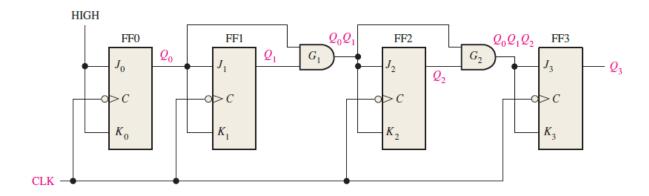

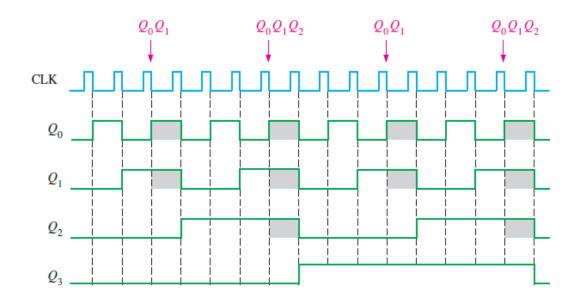

# A 3-Bit Synchronous Binary Counter

The state sequence for a 3-bit binary counter

| Clock Pulse  | Q2 | $Q_1$ | $Q_0$ |

|--------------|----|-------|-------|

| Initially    | 0  | 0     | 0     |

| 1            | 0  | 0     | 1     |

| 2            | 0  | 1     | 0     |

| 3            | 0  | 1     | 1     |

| 4            | 1  | 0     | 0     |

| 5            | 1  | 0     | 1     |

| 6            | 1  | 1     | 0     |

| 7            | 1  | 1     | 1     |

| 8 (recycles) | 0  | 0     | 0     |

# A 4-Bit Synchronous Binary Counter

# **Design of Synchronous Counters**

In this section, you will learn the six steps to design a counter (state machine).

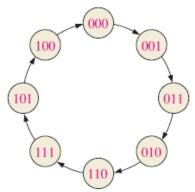

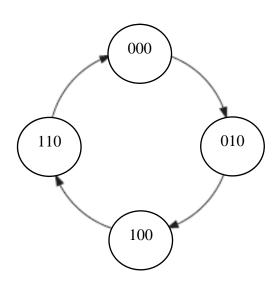

#### Step 1: State Diagram

The first step in the design of a state machine (counter) is to create a state diagram. A state diagram shows the progression of states through which the counter advances when it is clocked.

### Step 2: Next-State Table

Once the sequential circuit is defined by a state diagram, the second step is to derive a next-state table, which lists each state of the counter (present state) along with the corresponding next state. The next state is the state that the counter goes to from its present state upon application of a clock pulse. The next-state table is derived from the state diagram.

Next-state table for 3-bit Gray code counter.

|       | Present State | e     |                | Next State |       |

|-------|---------------|-------|----------------|------------|-------|

| $Q_2$ | $Q_1$         | $Q_0$ | $\mathbf{Q}_2$ | $Q_1$      | $Q_0$ |

| 0     | 0             | 0     | 0              | 0          | 1     |

| 0     | 0             | 1     | 0              | 1          | 1     |

| 0     | 1             | 1     | 0              | 1          | 0     |

| 0     | 1             | 0     | 1              | 1          | 0     |

| 1     | 1             | 0     | 1              | 1          | 1     |

| 1     | 1             | 1     | 1              | 0          | 1     |

| 1     | 0             | 1     | 1              | 0          | 0     |

| 1     | 0             | 0     | 0              | 0          | 0     |

#### Step 3: Flip-Flop Transition Table

Table below is a transition table for the J-K flip-flop. All possible output transitions are listed by showing the Q output of the flip-flop going from the present states to the next states.  $Q_N$  is the present state of the flip-flop (before a clock pulse) and QN + 1 is the next state (after a clock pulse). For each output transition, the J and K inputs that will cause the transition to occur are listed. An X indicates a "don't care" (the input can be either a 1 or a 0).

*Transition table for a J-K flip-flop*

| Output Transitions |           | Flip-Flop Inputs |   |  |

|--------------------|-----------|------------------|---|--|

| Qn                 | $Q_{n+1}$ | J                | K |  |

| 0 —                | 0         | 0                | X |  |

| 0 —                | 1         | 1                | X |  |

| 1 —                | 0         | X                | 1 |  |

| 1 —                | 1         | X                | 0 |  |

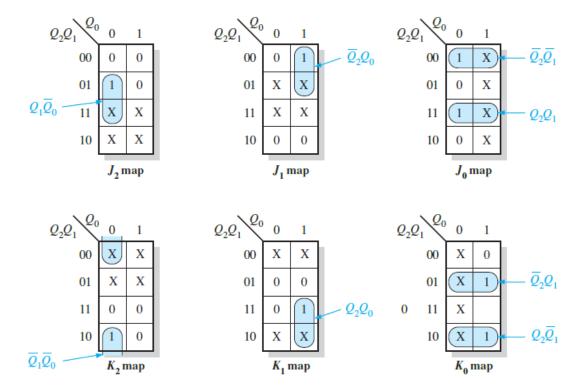

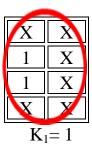

Step 4: Karnaugh Maps

Karnaugh maps can be used to determine the logic required for the J and K inputs of each flip-flop in the counter. There is a Karnaugh map for the J input and a Karnaugh map for the K input of each flip-flop. In this design procedure, each cell in a Karnaugh map represents one of the present states in the counter sequence listed in the above table. From the J and K states in the transition table, a 1, 0, or X is entered into each present-state cell on the maps depending on the transition of the Q output for a particular flip-flop.

#### Department of Biomedical Engineering Digital Electronics / Third stage Lecturer: Dr. Hussam Jawad Kadhim AL\_Janabi

Email: hussam.jawad@uomus.edu.iq

Step 5: Logic Expressions for Flip-Flop Inputs

$$J_{0} = Q_{2}Q_{1} + \overline{Q}_{2}\overline{Q}_{1} = \overline{Q_{2} \oplus Q_{1}}$$

$$K_{0} = Q_{2}\overline{Q}_{1} + \overline{Q}_{2}Q_{1} = Q_{2} \oplus Q_{1}$$

$$J_{1} = \overline{Q}_{2}Q_{0}$$

$$K_{1} = Q_{2}Q_{0}$$

$$J_{2} = Q_{1}\overline{Q}_{0}$$

$$K_{2} = \overline{Q}_{1}\overline{Q}_{0}$$

# Department of Biomedical Engineering Digital Electronics / Third stage Lecturer: Dr. Hussam Jawad Kadhim AL\_Janabi

Email: hussam.jawad@uomus.edu.iq

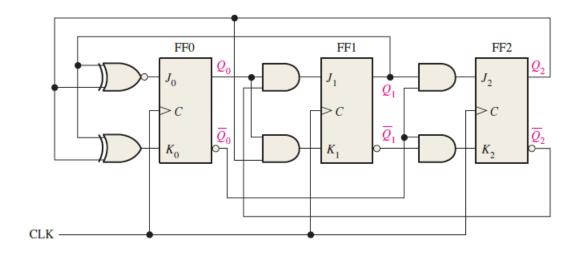

Step 6: Counter Implementation

Example: Design a 3-bit synchronous even counter

**Solution**

Step 1: State Diagram

### Department of Biomedical Engineering Digital Electronics / Third stage Lecturer: Dr. Hussam Jawad Kadhim AL\_Janabi

A MUSTICON JULY DE LA MUSTICON DE LA

Email: hussam.jawad@uomus.edu.iq

Step 2: Next-State Table

Step 3: Flip-Flop Transition Table

| Pr             | esent Sta      | ate            | N              | Vext State | e I.           |            | I. K.                 |    | $oldsymbol{V}_{+}$ | L           | V.          |

|----------------|----------------|----------------|----------------|------------|----------------|------------|-----------------------|----|--------------------|-------------|-------------|

| $\mathbf{Q}_2$ | $\mathbf{Q}_1$ | $\mathbf{Q}_0$ | $\mathbf{Q}_2$ | $Q_1$      | $\mathbf{Q}_0$ | <b>J</b> 2 | <b>K</b> <sub>2</sub> | J1 | <b>K</b> 1         | <b>J</b> () | <b>N</b> () |

| 0              | 0              | 0              | 0              | 1          | 0              | 0          | X                     | 1  | X                  | 0           | X           |

| 0              | 1              | 0              | 1              | 0          | 0              | 1          | X                     | X  | 1                  | 0           | X           |

| 1              | 0              | 0              | 1              | 1          | 0              | X          | 0                     | 1  | X                  | 0           | X           |

| 1              | 1              | 0              | 0              | 0          | 0              | X          | 1                     | X  | 1                  | 0           | X           |

| Output Transitions |           | Flip-Flop Inputs |   |  |

|--------------------|-----------|------------------|---|--|

| Qn                 | $Q_{n+1}$ | J                | K |  |

| 0                  | 0         | 0                | X |  |

| 0                  | 1         | 1                | X |  |

| 1                  | 0         | X                | 1 |  |

| 1                  | 1         | X                | 0 |  |

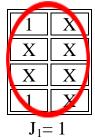

Step 4: Karnaugh Maps and Step 5: Logic Expressions for Flip-Flop Inputs

| X           | X |  |

|-------------|---|--|

| X           | X |  |

| 1           | X |  |

| 0           | X |  |

| $K_2 = Q_1$ |   |  |

| 0         | X |  |

|-----------|---|--|

| 0         | X |  |

| 0         | X |  |

| 0         | X |  |

| $J_0 = 0$ |   |  |

Step 6: Counter Implementation