## Communication Technical Engineering Department 1<sup>st</sup> Stage Digital Logic- UOMU028021 Lecture 4 – Identify the Logic Gates

Dr. Mohammed Fadhil PhD in Computer Networks Email: mohammed.fadhil1@uomus.edu.iq

Al Mustaqbal University - Communication Technical Engineering Department

#### **The Inverter**

- The inverter (NOT circuit) performs the operation called inversion or complementation. The inverter changes one logic level to the opposite level. In terms of bits, it changes a 1 to a 0 and a 0 to a 1.

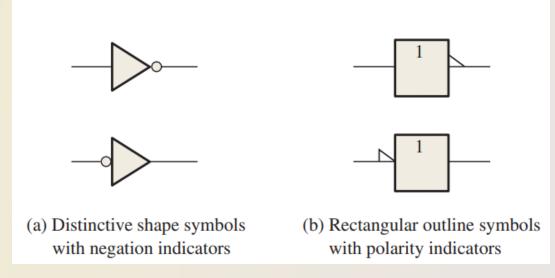

- Standard logic symbols for the inverter are shown in the following.

Al Mustaqbal University - Communication Technical Engineering Department

## **The Negation and Polarity Indicators**

- Negation Indicator (Bubble "○"):

- On input: Means a 0 is the active (asserted) state

→ Active-LOW input.

- On output: Means a 0 is the active (asserted) state  $\rightarrow$  Active-LOW output.

- − No bubble means 1 is active  $\rightarrow$  Active-HIGH.

- Polarity Indicator (Triangle "▷"):

- Same as the bubble—indicates LOW is the active state (asserted level).

- On input: Active-LOW input.

- On output: Active-LOW output.

- Key Points:

- Both bubbles and triangles mean the same thing (inversion/active-LOW).

- Placement (input/output) doesn't change how the logic element works.

- Used in all logic symbols (rectangular or shaped symbols).

- Example (Inverter):

- With bubble (○): Input 1 → Output

0, Input 0 → Output 1.

- With triangle (▷): Same as

bubble—just a different notation.

- Simple Rule:

- Bubble/Triangle = LOW is active (0 = ON).

- No Bubble/Triangle = HIGH is active (1 = ON).

# **Inverter Truth Table**

- When a HIGH level is applied to an inverter input, a LOW level will appear on its output.

- When a LOW level is applied to its input, a HIGH will appear on its output.

- This operation is summarized in the following Table, which shows the output for each possible input in terms of levels and corresponding bits. A table such as this is called a truth table.

| Inverter trut       | h table.            |

|---------------------|---------------------|

| Input               | Output              |

| LOW (0)<br>HIGH (1) | HIGH (1)<br>LOW (0) |

#### **Inverter Operation**

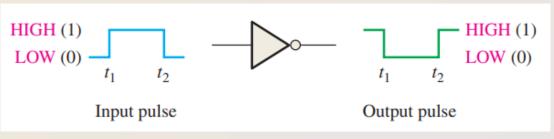

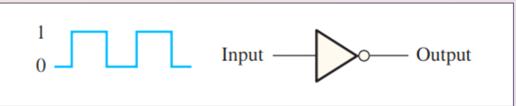

- Figure shows how an inverter works with a pulse input:

- When input is LOW (0)  $\rightarrow$  Output is HIGH (1).

- When input is HIGH (1) → Output is LOW (0).

- This inverts the input signal, flipping the pulse waveform.

- Points t<sub>1</sub> and t<sub>2</sub> mark corresponding transitions on the input and output pulses.

- The output is always the opposite (negation) of the input at every point in time.

**Inverter operation with a pulse input**

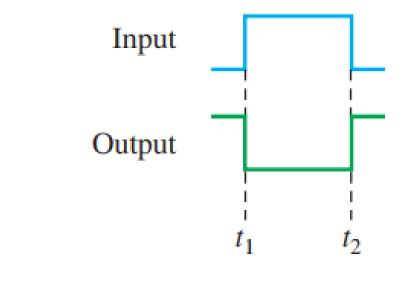

# **Timing Diagrams**

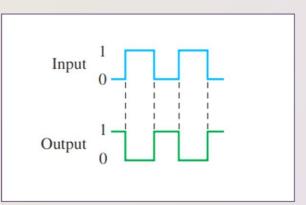

- A timing diagram is a graph that shows how digital signals (waveforms) change over time and how they relate to each other.

- Example: Inverter Timing

- When the input pulse goes HIGH (rising edge), the output pulse goes LOW (falling edge) at the same time (ideally).

- When the input pulse goes LOW (falling edge), the output pulse goes HIGH (rising edge) at the same time (ideally).

#### A timing diagram shows how two or more waveforms relate in time.

#### **EXAMPLE**

A waveform is applied to an inverter in the figure below. Determine the output waveform corresponding to the input and show the timing diagram. According to the placement of the bubble, what is the active output state?

#### Solution

The output waveform is exactly opposite to the input (inverted), as shown in the following Figure, which is the basic timing diagram. The active or asserted output state is 0.

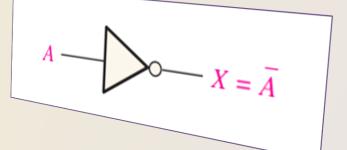

# **Logic Expression for an Inverter**

#### Variables & Notation:

- Variables represent inputs/outputs in logic circuits (e.g., A, B for inputs; X, Y for outputs).

- A complement (inverse) is shown with a bar:

- If A = 1, then Ā = 0 (and vice versa).

- Inverter (NOT Gate) Operation:

- If input = A and output = X, then:

X = A

- This means:

- When **A** = 0, **X** = 1.

- When **A** = 1, **X** = 0.

- Example:

- If A is HIGH (1), the inverter outputs LOW (0).

- If A is LOW (0), the inverter outputs HIGH (1).

Boolean algebra uses variables and operators to describe a logic circuit.

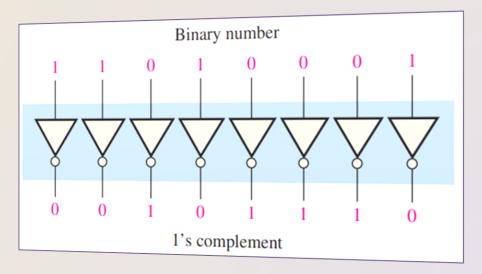

## **An Application**

The Figure below shows a circuit for producing the 1's complement of an 8-bit binary number. The bits of the binary number are applied to the inverter inputs and the 1's complement of the number appears on the outputs.

### **CHECKUP!**

- Answers are at the end of the chapter.

- 1. When a 1 is on the input of an inverter, what is the output?

- 2. An active-HIGH pulse (HIGH level when asserted, LOW level when not) is required on an inverter input.

- a) Draw the appropriate logic symbol, using the distinctive shape and the negation indicator, for the inverter in this application.

- b) Describe the output when a positive-going pulse is applied to the input of an inverter.

## **The AND Gate**

- The AND gate is one of the basic gates that can be combined to form any logic function.

- An AND gate can have two or more inputs and performs what is known as logical multiplication

- The AND gate is a basic logic gate with:

- Two or more inputs (left side of symbol).

- One output (right side of symbol).

- Key Characteristics:

- Output Rule:

- The output is HIGH (1) only if ALL inputs are HIGH (1).

- Otherwise, the output is LOW (0).

- Number of Inputs:

- Typically shown with 2 inputs, but can have more than two inputs.

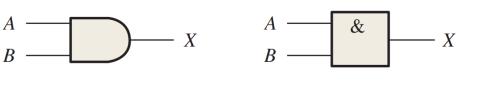

- Logic Symbols:

- Distinctive shape (traditional)

- Rectangular outline (IEEE standard)

(a) Distinctive shape

(b) Rectangular outline with the AND (&) qualifying symbol

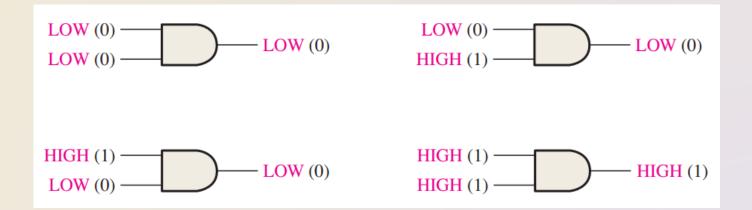

## **Operation of an AND Gate**

- An AND gate produces a HIGH (1) output only when all its inputs are HIGH. If any input is LOW (0), the output is LOW.

- Key Behavior (2-Input AND Gate):

- Output (X) is HIGH only if:

- A = 1 AND B = 1.

- Output (X) is LOW if:

- A = 0,

- B = 0,

- or both A and B = 0.

## **AND Gate Truth Table**

- Core Concept

- An AND gate outputs 1 (HIGH) only when all inputs are 1. Otherwise, it outputs 0 (LOW).

- Truth Table for 2-Input AND Gate

- Key Features

- Input Combinations:

- For \*n\* inputs, there are 2<sup>n</sup> possible combinations.

- Examples:

- 2 inputs  $\rightarrow$  4 combinations (2<sup>2</sup>)

- 3 inputs  $\rightarrow$  8 combinations (2<sup>3</sup>)

- 4 inputs  $\rightarrow$  16 combinations (2<sup>4</sup>)

| Truth<br>AND g |      | a 2-input |

|----------------|------|-----------|

| Inp            | outs | Output    |

| A              | В    | X         |

| 0              | 0    | 0         |

| 0              | 1    | 0         |

| 1              | 0    | 0         |

| 1              | 1    | 1         |

#### **EXAMPLE**

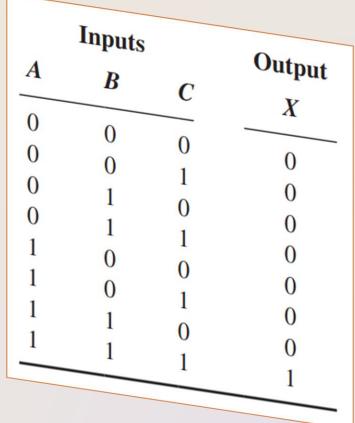

- A. Develop the truth table for a 3-input AND gate.

- B. Determine the total number of possible input combinations for a 4-input AND gate.

- Solution

- A. There are eight possible input combinations  $(2^3 = 8)$  for a 3-input AND gate. The input side of the truth table shows all eight combinations of three bits. The output side is all 0s except when all three input bits are 1s.

- B.  $N = 2^4 = 16$ . There are 16 possible combinations of input bits for a 4-input AND gate.

- Related Problem

- **Develop the truth table for a 4-input AND gate.**

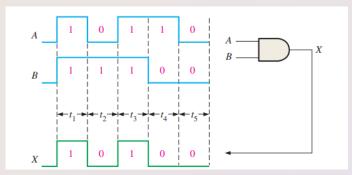

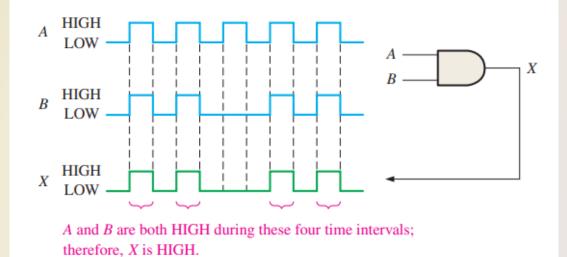

## **AND Gate Operation with Waveform Inputs**

- An AND gate follows its truth table logic regardless of whether its inputs are constant levels or changing pulse waveforms.

- The output is HIGH (1) only when all inputs are HIGH (1) at the same time; otherwise, it remains LOW (0).

- Timing Analysis (as described in the Figure):

- Interval t<sub>1</sub>: Both inputs A and B are HIGH (1)  $\rightarrow$  Output X is HIGH (1).

- Interval t<sub>2</sub>: A = LOW (0), B = HIGH (1) → Output X is LOW (0).

- Interval t<sub>3</sub>: Both A and B are HIGH (1) → Output X is HIGH (1).

- Interval t<sub>4</sub>: A = HIGH (1), B = LOW (0) → Output X is LOW (0).

- Interval t<sub>5</sub>: Both A and B are LOW (0) → Output X is LOW (0).

- A timing diagram visually represents these input-output relationships over time, showing how the AND gate responds to changing input waveforms.

If two waveforms, A and B, are applied to the AND gate inputs as in the below Figure, what is the resulting output waveform?

#### Solution

The output waveform X is HIGH only when both A and B waveforms are HIGH as shown in the timing diagram.

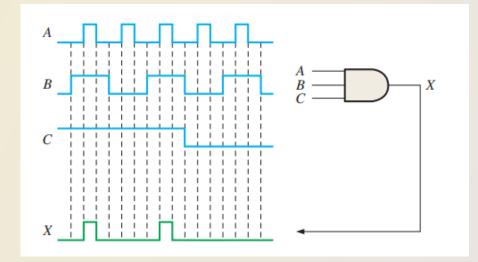

For the 3-input AND gate in the below Figure, determine the output waveform in relation to the inputs.

#### Solution

The output waveform X of the 3-input AND gate is HIGH only when all three input waveforms A, B, and C are HIGH.

## **Logic Expressions for an AND Gate**

- The logical AND function of two variables is represented mathematically either by placing a dot between the two variables, as A . B, or by simply writing the adjacent letters without the dot, as AB.

- Boolean multiplication follows the same basic rules governing binary multiplication:

- $0 \cdot 0 = 0$  $0 \cdot 1 = 0$  $1 \cdot 0 = 0$  $1 \cdot 1 = 1$

## **Logic Expressions for an AND Gate**

- Boolean multiplication is the same as the AND function.

- The operation of a 2-input AND gate can be expressed in equation form as follows:

- If one input variable is A, if the other input variable is B, and if the output variable is X, then the Boolean expression is: X = AB

| A | B | AB = X          |

|---|---|-----------------|

| 0 | 0 | $0 \cdot 0 = 0$ |

| 0 | 1 | $0 \cdot 1 = 0$ |

| 1 | 0 | $1 \cdot 0 = 0$ |

| 1 | 1 | $1 \cdot 1 = 1$ |

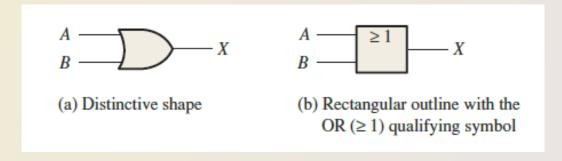

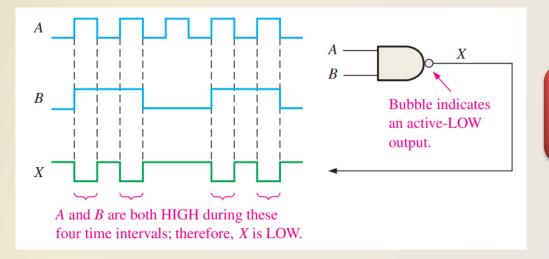

#### **The OR Gate**

- The OR gate is another of the basic gates from which all logic functions are constructed.

- An OR gate can have two or more inputs and performs what is known as logical addition.

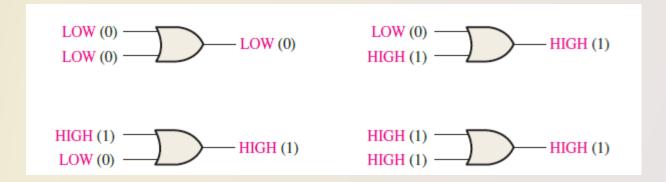

## **Operation of an OR Gate**

- For an OR gate, at least one HIGH input produces a HIGH output.

- For a 2-input OR gate,

- output X is HIGH when either input A or input B is HIGH, or when both A and B are HIGH;

- X is LOW only when both A and B are LOW.

Al Mustaqbal University - Communication Technical Engineering Department

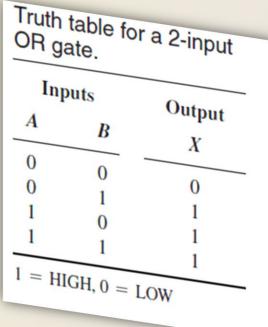

## **OR Gate Truth Table**

The operation of a 2-input OR gate is described in Table. This truth table can be expanded for any number of inputs; but regardless of the number of inputs, the output is HIGH when one or more of the inputs are HIGH.

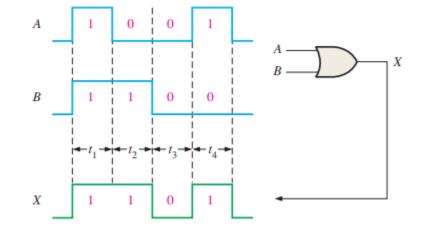

## **OR Gate Operation with Waveform Inputs**

- Time Interval t<sub>1</sub>: A=1, B=1  $\rightarrow$  X=1

- Time Interval t<sub>2</sub>: A=0, B=1  $\rightarrow$  X=1

- Time Interval t<sub>3</sub>: A=0, B=0  $\rightarrow$  X=0

- Time Interval t<sub>4</sub>: A=1, B=0  $\rightarrow$  X=1

- Key Point:

- Output (X) is HIGH (1) if at least one input is HIGH (1).

- In this figure, we have applied the truth table operation of the OR gate to each of the time intervals.

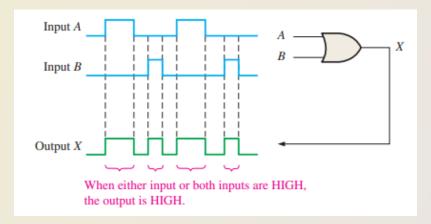

• If the two input waveforms, A and B, in the below Figure are applied to the OR gate, what is the resulting output waveform?

#### Solution

The output waveform X of a 2-input OR gate is HIGH when either or both input waveforms are HIGH as shown in the timing diagram. In this case, both input waveforms are never HIGH at the same time.

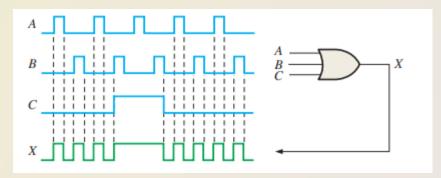

• For the 3-input OR gate in the below Figure, determine the output waveform in proper time relation to the inputs.

#### Solution

The output is HIGH when one or more of the input waveforms are HIGH as indicated by the output waveform X in the timing diagram.

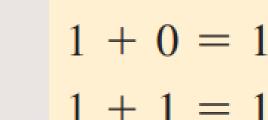

# **Logic Expressions for an OR Gate**

- The logical OR function of two variables is represented mathematically by a + between the two variables,

- for example, A + B. The plus sign is read as "OR."

- Addition in Boolean algebra involves variables whose values are either binary 1 or binary 0.

- The basic rules for Boolean addition are as follows:

- When variables are separated by 1, they are ORed.

0 + 0 = 0

0 + 1 = 1

### **Boolean addition is the same as the OR function.**

- Notice that Boolean addition differs from binary addition in the case where two 1s are added. There is no carry in Boolean addition.

- The operation of a 2-input OR gate can be expressed as follows:

- If one input variable is A, if the other input variable is B, and if the output variable is X, then the Boolean expression i: A = B = A + B = X

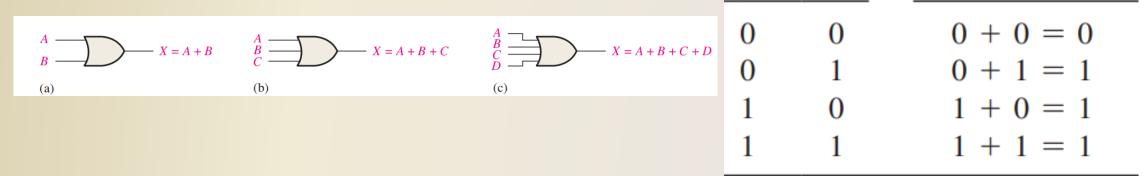

### **The NAND Gate**

- The NAND gate is a popular logic element because it can be used as a universal gate; that is, NAND gates can be used in combination to perform the AND, OR, and inverter operations.

- The term NAND is a contraction of NOT-AND and implies an AND function with a complemented (inverted) output.

(a) Distinctive shape, 2-input NAND gate and its NOT/AND equivalent

(b) Rectangular outline, 2-input NAND gate with polarity indicator

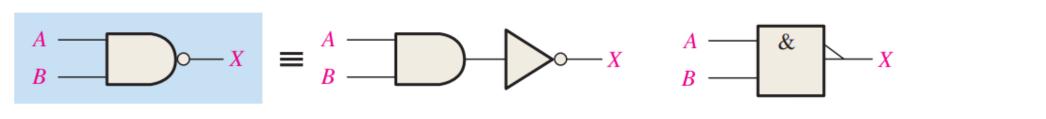

# **Operation of a NAND Gate**

- A NAND gate produces a LOW output only when all the inputs are HIGH. When any of the inputs is LOW, the output will be HIGH.

- For a 2-input NAND gate,

- output X is LOW only when inputs A and B are HIGH;

- X is HIGH when either A or B is LOW, or when both A and B are LOW.

- This operation is opposite that of the AND in terms of the output level.

Truth table for a 2-input NAND gate.

| Inputs |   | Output |

|--------|---|--------|

| A      | B | X      |

| 0      | 0 | 1      |

| 0      | 1 | 1      |

| 1      | 0 | 1      |

| 1      | 1 | 0      |

1 = HIGH, 0 = LOW.

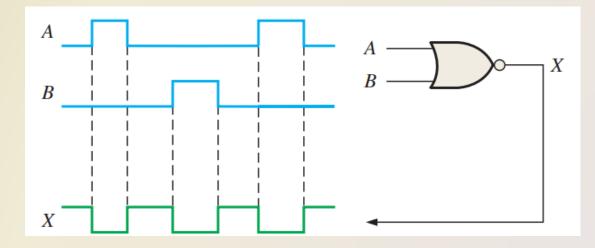

## **NAND Gate Operation with Waveform Inputs**

#### • EXAMPLE:

Solution:

If the two waveforms A and B shown in the below Figure are applied to the NAND gate inputs, determine the resulting output waveform.

Remember from the truth table that the only time a LOW output occurs is when all of the inputs are HIGH.

#### Output waveform X is LOW only during the four time intervals when both input waveforms A and B are HIGH as shown in the timing diagram.

### **Logic Expressions for a NAND Gate**

• The Boolean expression for the output of a 2-input NAND gate is

$$X = \overline{AB}$$

A bar over a variable or variables indicates an inversion

| A | B | $\overline{AB} = X$                       |

|---|---|-------------------------------------------|

| 0 | 0 | $\overline{0 \cdot 0} = \overline{0} = 1$ |

| 0 | 1 | $\overline{0 \cdot 1} = \overline{0} = 1$ |

| 1 | 0 | $\overline{1 \cdot 0} = \overline{0} = 1$ |

| 1 | 1 | $\overline{1\cdot 1}=\overline{1}=0$      |

#### **The NOR Gate**

- The NOR gate, like the NAND gate, is a useful logic element because it can also be used as a universal gate; that is, NOR gates can be used in combination to perform the AND, OR, and inverter operations.

- The term NOR is a contraction of NOT-OR and implies an OR function with an inverted (complemented) output. The standard logic symbol for a 2-input NOR gate and its equivalent OR gate followed by an inverter.

$$A = D - X = B = D - D - X = A = 21 - X$$

$$B = D - X = B = 21 - X$$

(a) Distinctive shape, 2-input NOR gate and its NOT/OR equivalent

(b) Rectangular outline, 2-input NOR gate with polarity indicator

## **Operation of a NOR Gate**

- A NOR gate produces a LOW output when any of its inputs is HIGH. Only when all of its inputs are LOW is the output HIGH.

- For a 2-input NOR gate,

- output X is LOW when either input A or input B is HIGH, or when both A and B are HIGH;

- X is HIGH only when both A and B are LOW.

Truth table for a 2-input NOR gate.

| Inputs |   | Output |

|--------|---|--------|

| A      | B | X      |

| 0      | 0 | 1      |

| 0      | 1 | 0      |

| 1      | 0 | 0      |

| 1      | 1 | 0      |

| 1      |   |        |

1 = HIGH, 0 = LOW.

### **NOR Gate Operation with Waveform Inputs**

#### • EXAMPLE:

If the two waveforms shown in Figure 3–36 are applied to a NOR gate, what is the resulting output waveform?

#### Solution

Whenever any input of the NOR gate is HIGH, the output is LOW as shown by the output waveform X in the timing diagram.

## **Logic Expressions for a NOR Gate**

- The Boolean expression for the output of a 2-input NOR gate can be written as:  $X = \overline{A + B}$

- This equation says that the two input variables are first ORed and then complemented, as indicated by the bar over the OR expression

| A | B | $\overline{A + B} = X$              |

|---|---|-------------------------------------|

| 0 | 0 | $\overline{0+0} = \overline{0} = 1$ |

| 0 | 1 | $\overline{0+1} = \overline{1} = 0$ |

| 1 | 0 | $\overline{1+0} = \overline{1} = 0$ |

| 1 | 1 | $\overline{1+1} = \overline{1} = 0$ |

### **The Exclusive-OR and Exclusive-NOR Gates**

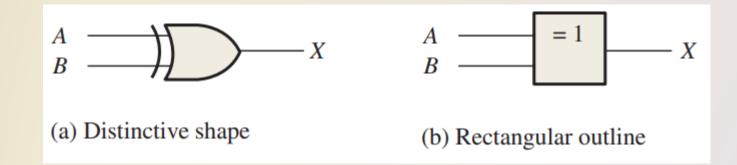

#### The Exclusive-OR Gate

- Standard symbols for an exclusive-OR (XOR for short) gate are shown below.

- The XOR gate has only two inputs. The output of an exclusive-OR gate is HIGH only when the two inputs are at opposite logic levels.

## **The Exclusive-OR Gate**

- For an exclusive-OR gate,

- output X is HIGH when input A is LOW and input B is HIGH, or when input A is HIGH and input B is LOW;

- X is LOW when A and B are both HIGH or both LOW.

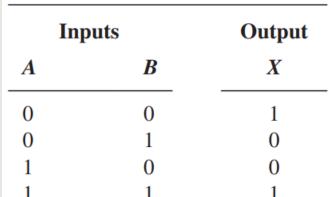

Truth table for an exclusive-OR gate.

| Inputs |   | Output |

|--------|---|--------|

| A      | B | X      |

| 0      | 0 | 0      |

| 0      | 1 | 1      |

| 1      | 0 | 1      |

| 1      | 1 | 0      |

Al Mustaqbal University - Communication Technical Engineering Department

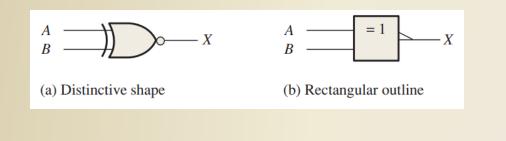

# **The Exclusive-NOR Gate**

- Standard symbols for an exclusive-NOR (XNOR) gate. Like the XOR gate, an XNOR has only two inputs. The bubble on the output of the XNOR symbol indicates that its output is opposite that of the XOR gate.

- For an exclusive-NOR gate,

- output X is LOW when input A is LOW and input B is HIGH, or when A is HIGH and B is LOW;

- X is HIGH when A and B are both HIGH or both LOW. NOR gate.

#### XOR gate used as a modulo-2 adder

An examination of the truth table for an XOR gate shows that its output is the binary sum of the two input bits. In the case where the inputs are both 1s, the output is the sum 0, but you lose the carry of 1.

|       | orrga  |                 | .0. |

|-------|--------|-----------------|-----|

| Input | t Bits | Output (Sum)    |     |

| A     | B      | Σ               |     |

| 0     | 0      | 0               |     |

| 0     | 1      | 1               |     |

| 1     | 0      | 1               |     |

| 1     | 1      | 0 (without      |     |

|       | )[     | the 1 carry bit | :)  |

**THANK YOU**