# Communication Technical Engineering Department 1<sup>st</sup> Stage Digital Logic- UOMU028021 Lecture 6 – Half-adder & Full-adder

Dr. Mohammed Fadhil PhD in Computer Networks Email: mohammed.fadhil1@uomus.edu.iq

#### Half-adder & Full-adder

- Adders are important in computers and also in other types of digital systems in which numerical data are processed. 0 + 0 = 0

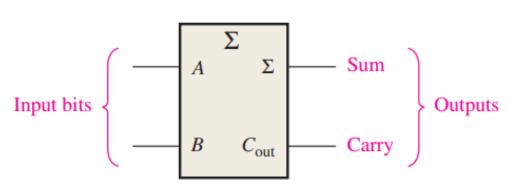

- A half-adder adds two bits and produces a <u>sum and an output carry.</u>

- The operations are performed by a logic circuit called a half-adder.

- 0 + 0 = 0

- 0 + 1 = 1

- 1 + 0 = 1

- 1 + 1 = 10

- The half-adder accepts two binary digits on its inputs and produces two binary digits on its outputs—a sum bit and a carry bit.

- A half-adder is represented by the logic symbol in the following Figure

# **Half-Adder Logic**

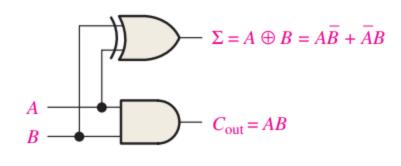

- From the operation of the half-adder as stated in the Table, expressions can be derived for the sum and the output carry as functions of the inputs.

- Notice that the output carry (C<sub>out</sub>) is a 1 only when both A and B are 1s; therefore, C<sub>out</sub> can be expressed as the AND of the input variables.

- $C_{out} = AB$

- Now observe that the sum output ∑ is a 1 only if the input variables, A and B, are not equal. The sum can therefore be expressed as the exclusive-OR of the input variables.

- A

B

Cout

0

0

0

0

0

Half-adder truth table.

$\Sigma = sum$

0

$C_{\rm out} = {\rm output \ carry}$

0

A and B = input variables (operands)

Σ

0

0

•  $\sum = A \oplus B$

# Half-Adder Logic

- The logic implementation required for the half-adder function can be developed. The output carry is produced with an AND gate with A and B on the inputs, and the sum output is generated with an exclusive-OR gate, as shown in the below Figure.

- Remember that the exclusive-OR can be implemented with AND gates, an OR gate, and inverters.

Half-adder logic diagram.

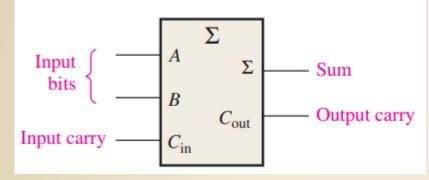

- The second category of adder is the full-adder.

- The full-adder accepts two input bits and an input carry and generates a sum output and an output carry.

- A full-adder has an input carry while the half-adder does not.

- A logic symbol for a full-adder is shown in Figure

#### Full-adder Truth Table Σ B Cout $C_{in}$ A 0 0 0 0 0 0 0 0 0 0 0 0

$C_{\rm in} =$  input carry, sometimes designated as CI $C_{\rm out} =$  output carry, sometimes designated as CO $\Sigma =$  sum

A and B = input variables (operands)

### **Full-Adder Logic**

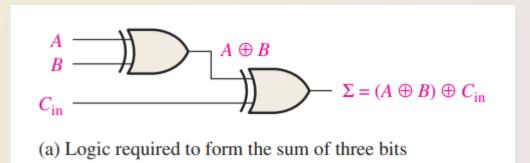

- The full-adder must add the two input bits and the input carry.

From the half-adder you know that the sum of the input bits A and

B is the exclusive-OR of those two variables, A ⊕ B.

- For the input carry (C<sub>in</sub>) to be added to the input bits, it must be exclusive-ORed with A ⊕ B, yielding the equation for the sum output of the full-adder.

- $\Sigma = (A \oplus B) \oplus C_{in}$

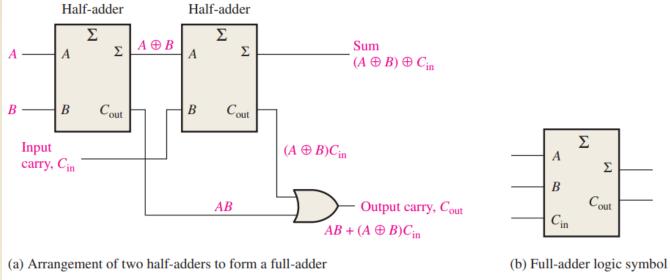

- This means that to implement the full-adder sum function, two 2input exclusive-OR gates can be used.

- The first must generate the term A ⊕ B, and the second has as its inputs the output of the first XOR gate and the input carry, as illustrated in Figure

- The output carry is a 1 when both inputs to the first XOR gate are 1s or when both inputs to the second XOR gate are 1s. You can verify this fact by studying full adder truth Table.

- These two terms are ORed, as expressed in Equation:

C<sub>out</sub> = AB + (A ⊕ B) C<sub>in</sub>

- This function is implemented and combined with the sum logic to form a complete full-adder circuit.

There are two half-adders, connected as shown in the block diagram of Figure (a), with their output carries ORed. The logic symbol shown in Figure (b) will normally be used to represent the full-adder.

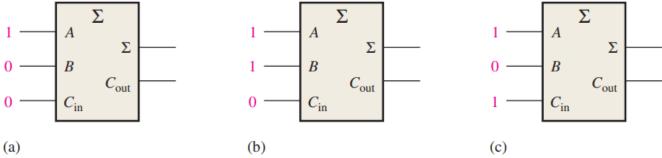

For each of the three full-adders in Figure a,b,c, determine the outputs for the inputs shown.

#### Solution

```

- (a) The input bits are A = 1, B = 0, and C_{in} = 0.

1 + 0 + 0 = 1 with no carry

Therefore, \sum = 1 and C_{out} = 0.

- (b) The input bits are A = 1, B = 1, and C_{in} = 0.

1 + 1 + 0 = 0 with a carry of 1

Therefore, \sum = 0 and C_{out} = 1.

- (c) The input bits are A = 1, B = 0, and Cin = 1.

1 + 0 + 1 = 0 with a carry of 1

Therefore, \sum = 0 and C_{out} = 1.

```

#### **Checkup!**

Determine the sum (∑) and the output carry (C<sub>out</sub>) of a half-adder for each set of input bits:

– (a) 01 (b) 00 (c) 10 (d) 11

A full-adder has C<sub>in</sub> = 1. What are the sum (∑) and the output carry (C<sub>out</sub>) when A = 1 and B = 1?

#### **Solution**

#### • Solving Part (a): Input Bits 01

- Inputs: A = 0, B = 1

- Calculate Sum ( $\Sigma$ ):

- A XOR B = 0 XOR 1

- 0 XOR 1 = 1

- Calculate Carry-out (C<sub>out</sub>):

- A AND B = 0 AND 1

- 0 AND 1 = 0

- Answer:

- Sum (∑) = 1

- $-C_{out} = 0$

A full-adder has  $C_{in} = 1$ . What are the sum ( $\sum$ ) and the output carry ( $C_{out}$ ) when A = 1 and B = 1?

- Solving the Full-Adder Problem

- Given:

- A = 1, B = 1, C\_in = 1

- Step 1: Calculate A  $\oplus$  B:

- $A \bigoplus B = 1 \bigoplus 1 = 0$

- Step 2: Plug into the formula

- Cout=AB+(A⊕B)·Cin =(1·1)+(0·1) =1+0=1

- Sum (Σ) is still:

- $\Sigma = A \bigoplus B \bigoplus Cin$ =1  $\bigoplus 1 \bigoplus 1$ =0  $\bigoplus 1 = 1$

- Final Answer:

- Sum (∑) = 1

- C\_out = 1

**THANK YOU**