## Propagation Delay in Ripple Counters

### **What is Propagation Delay?**

**Propagation delay** is the *time it takes for a change at the input of a flip-flop to cause a change at its output.*

Each flip-flop in a counter takes a **small amount of time ( $\Delta t$ )** to respond to a clock pulse.

### **Example:**

If a flip-flop takes **25 ns (nanoseconds)** to change its output after receiving a clock pulse, then **its propagation delay = 25 ns.**

## **What Happens in Ripple Counters?**

A **ripple counter** is a type of **asynchronous counter**, meaning not all flip-flops are clocked at the same time.

The **first flip-flop (FF<sub>0</sub>)** receives the external clock directly.

The **second flip-flop (FF<sub>1</sub>)** receives the output of FF<sub>0</sub> as its clock input.

The **third flip-flop (FF<sub>2</sub>)** is clocked by FF<sub>1</sub>, and so on.

Thus, the **clock signal "ripples"** through the flip-flops — one after another.

## How Propagation Delay Accumulates?

**Total delay =  $n \times tpd$ ,**

where **n** = number of flip-flops, **tpd** = propagation delay of one flip-flop.

Each flip-flop introduces a small delay. So, if you have multiple flip-flops connected in sequence:

| Flip-Flop       | Trigger Source            | Delay Added | Cumulative Delay |

|-----------------|---------------------------|-------------|------------------|

| FF <sub>0</sub> | External Clock            | tpd         | tpd              |

| FF <sub>1</sub> | Output of FF <sub>0</sub> | tpd         | 2 × tpd          |

| FF <sub>2</sub> | Output of FF <sub>1</sub> | tpd         | 3 × tpd          |

| FF <sub>3</sub> | Output of FF <sub>2</sub> | tpd         | 4 × tpd          |

## Propagation Delay in Ripple Counters

How Propagation Delay Accumulates?

**Example:** Suppose a 4-bit ripple counter is built using flip-flops with: Propagation delay per flip-flop = 25 ns.

Then:

Total propagation delay =  $4 \times 25 \text{ ns} = 100 \text{ ns}$ .

So, the output will be fully stable **100 ns after** the clock pulse.

Propagation Delay in Ripple Counters:

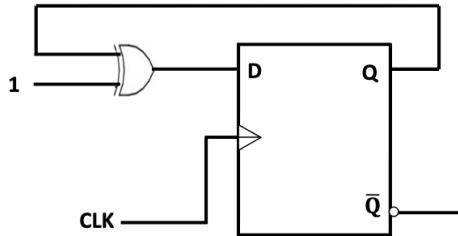

Fig 1 Toggle D flip-flop

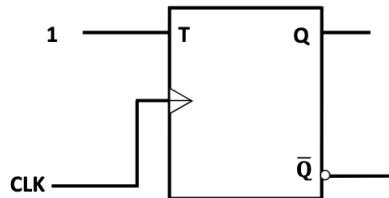

Fig 2 Toggle T flip-flop

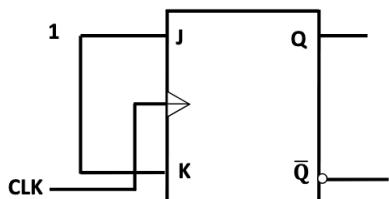

Fig 3 Toggle J-K flip-flop

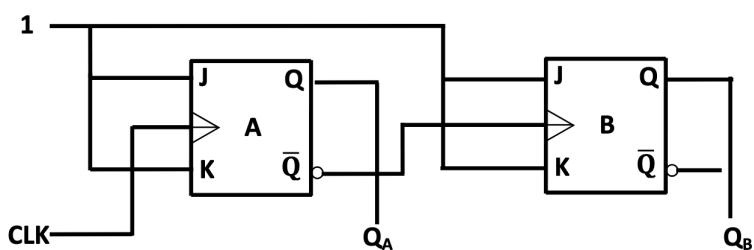

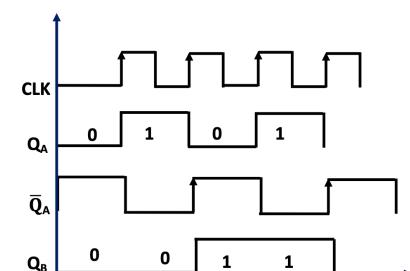

**Example:** Design 2-bits up (**ripple counter**) asynchronous counter using J-K flip-flops with a positive edge clock pulse.

Answer:

| B | A | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 2      |

| 1 | 1 | 3      |

### **Modulus (MOD):**

Modulus (MOD) – the number of states it counts in a complete cycle before it goes back to the initial state. Thus, the number of flip-flops used depends on the MOD of the counter (ie; MOD-4 use 2 FF (2-bit), MOD-8 use 3 FF (3-bit), etc..)

Example: MOD-4 Ripple/Asynchronous Up-Counter.

If a counter has **n flip-flops**, each flip-flop can store 2 states (0 or 1).

$$\text{MOD} = 2^n$$

- ❖ **n = number of flip-flops (bits)**

- ❖ **MOD = total number of counts**

### **Modulus Counters**

#### **Maximum Count (N)**

The maximum count of the counter is related to the number of (flip-flops) that build the counter which can be expressed as:  $N = 2^n - 1$

For example, for four flip-flops, the maximum count is  $N = 2^4 - 1 = 15$  which is equivalents to (1111) in the binary system.

| Number of Flip-Flops (n) | Counter Type  | Counting Range     | MOD Value |

|--------------------------|---------------|--------------------|-----------|

| 1                        | 1-bit counter | $0 \rightarrow 1$  | MOD-2     |

| 2                        | 2-bit counter | $0 \rightarrow 3$  | MOD-4     |

| 3                        | 3-bit counter | $0 \rightarrow 7$  | MOD-8     |

| 4                        | 4-bit counter | $0 \rightarrow 15$ | MOD-16    |

This type of counter is used when the application needs certain count such as to (1001). These counters are built by controlling the clear element of the flip-flops thus when reach the required count clear all flip-flops of the counter.

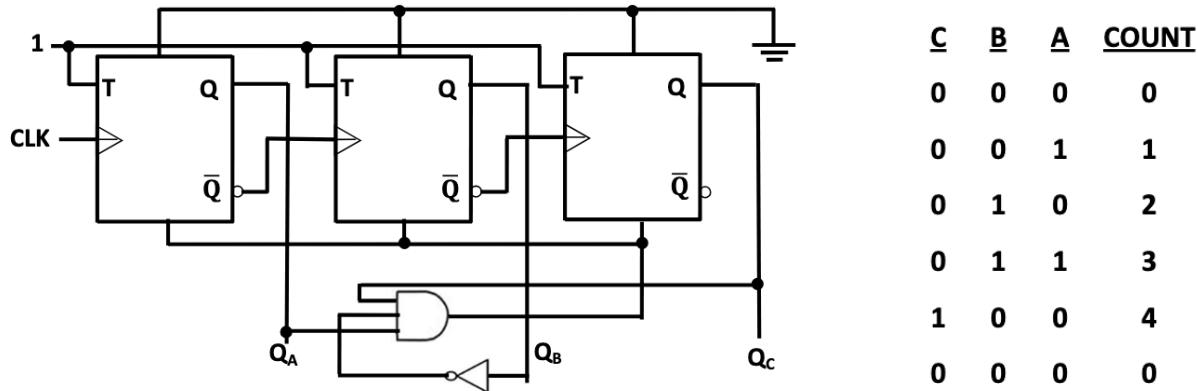

**Example: design (Mod 5) up counter using T flip-flops using AND gate as control element.**

**Classwork during the Lab:**

Design a (Mod 8) up counter using D flip-flops with a negative edge clock pulse. Draw the timing diagram and truth table for this counter.

**Homework:**

Design a (Mod 11) up counter using T flip-flops with negative edge clock pulse, use NAND gate as a control unit. Draw the timing diagram and truth table for this counter.